#### **Features**

- Universal: Dual Low-Side, Dual High-Side or Half-Bridge Driver

- Operating Temperature Range –40 to +125°C

- Switching Parameters:

- 19-ns Typical Propagation Delay

- ➢ 10-ns Minimum Pulse Width

- > 5-ns Maximum Delay Matching

- > 5-ns Maximum Pulse-Width Distortion

- Common-Mode Transient Immunity (CMTI): 100kV/us

- Isolation Barrier Life >40 Years

- 4-A Peak Source, 8-A Peak Sink Output

- TTL and CMOS Compatible Inputs

- 3V to 5.5V Input VCCI Range to Interface with Both Digital and Analog Controllers

- Up to 25V VDD Output Drive Supply

- Programmable Overlap and Dead Time

- Rejects Input Pulses and Noise Transients Shorter than

Sns

- Fast Disable for Power Sequencing

- Safety-Related Certifications:

- 5000V<sub>PK</sub> Basic Isolation per DIN EN IEC 60747-17

(VDE 0884-17) :2021-10

- **5kV**<sub>RMS</sub> Isolation for 1 Minute per UL 1577

- > CSA Certification per IEC 60950-1, IEC 62368-1,

- IEC 61010-1 and IEC 60601-1 End Equipment Standards

- CQC Certification per GB4943.1-2022

- RoHS-compliant, NB SOIC-16 package and WB SOIC-14

# **Applications**

- HEV and BEV Battery Chargers

- Isolated Converters in DC-DC and AC-DC Power Supplies

- Server, Telecom, IT and Industrial Infrastructures

- Motor Drive and DC-to-AC Solar Inverters

- LED Lighting

- Inductive Heating

- Uninterruptible Power Supply (UPS)

# **General Description**

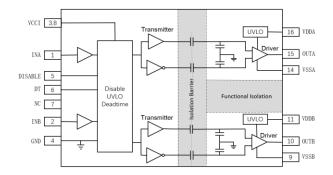

The Pai8232B/C and Pai8233B/C are the dual-channel isolated gate drivers based on *iDivider*<sup>®</sup> technology of 2Pai Semi. It has a source peak current of 4A and a sink peak current of 8A. The maximum switching frequency can reach 5MHz. It is suitable for gate drive of MOSFET, IGBT and SiC MOSFET.

The input side is isolated from the two output sides by an isolation barrier that can withstand  $3k/5kV_{RMS}$  isolation voltage,

responsibility is assumed by 2Pai semi for its use, nor for any infringements of patents or

other rights of third parties that may result from its use. Specifications subject to change

without notice. No license is granted by implication or otherwise under any patent or patent

and the typical common-mode transient immunity (CMTI) capability is 100kV/us. The internal functional isolation between the two secondary side drivers allows a maximum operating voltage of  $1200V_{DC}$ .

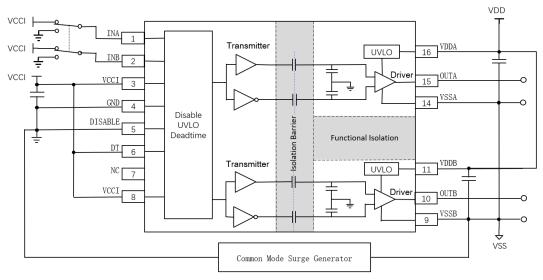

Every driver can be configured as two low-side drivers, two high-side drivers, or a half-bridge driver with programmable dead time (DT). A disable pin shuts down both outputs simultaneously when it is set high and allows normal operation when left open or grounded. As a fail-safe measure, primaryside logic failures force both outputs low.

Each device accepts VDD supply voltages up to 25V. A wide input VCCI range from 3V to 5.5V makes the driver suitable for interfacing with both analog and digital controllers. All the supply voltage pins have under voltage lock-out (UVLO) protection.

#### **Device Information**

| Part Number                | Isolation<br>Rating | Rec. VDD<br>Supply Min. | Package    |

|----------------------------|---------------------|-------------------------|------------|

| Pai823XB-WR <sup>1</sup>   | 5kV                 | 6.5V                    | WB SOIC-14 |

| Pai823XB-S1R <sup>1</sup>  | 3KV                 | 6.5V                    | NB SOIC-16 |

| Pai823XC-WR <sup>1</sup>   | 5KV                 | 9.2V                    | WB SOIC-14 |

| Pai823XC-S1R <sup>1</sup>  | 3KV                 | 9.2V                    | NB SOIC-16 |

| Pai823xBQ-WR <sup>2</sup>  | 5KV                 | 6.5V                    | WB SOIC-14 |

| Pai823xBQ-S1R <sup>2</sup> | 3KV                 | 6.5V                    | NB SOIC-16 |

| Pai823xCQ-WR <sup>2</sup>  | 5KV                 | 9.2V                    | WB SOIC-14 |

| Pai823xCQ-S1R <sup>2</sup> | 3KV                 | 9.2V                    | NB SOIC-16 |

Note:

- 1) "X" in part number means Ipk. 2 for 2A/4A, 3 for 4A/8A

- 2) AEC-Q100 qualified for automotive application

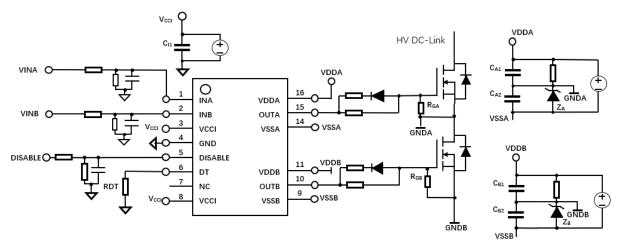

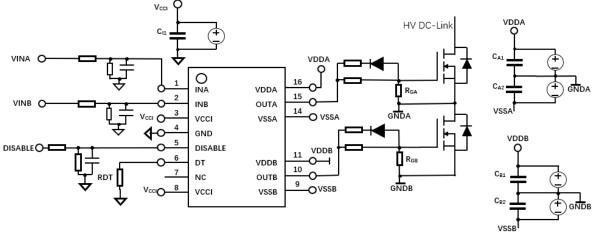

# **Functional Block Diagram**

Fig 1.Pai8232B/C and Pai8233B/C Functional Block Diagram

Room 307-309, No.22, Boxia Road, Pudong New District, Shanghai, 201203, China 021-50850681 2Pai Semiconductor Co., Limited. All rights reserved. http://www.rpsemi.com/

rights of 2Pai semi. Trademarks and registered trademarks are the property of their respective owners.

Rev 1.2 Information furnished by 2Pai semi is believed to be accurate and reliable. However, no

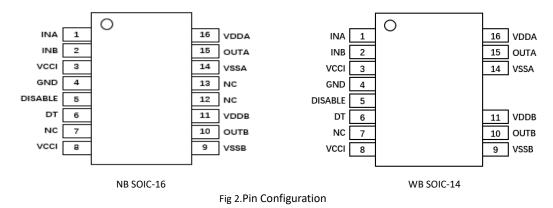

# 1. Pin Configurations and Functions

Table 1.Pai8232B/C and Pai8233B/C Pin Function Descriptions

| PIN     | PIN        | NO.        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                             |

|---------|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME    | NB SOIC-16 | WB SOIC-14 |                                                                                                                                                                                                                                                                                                                                                                         |

| INA     | 1          | 1          | Input signal for A channel.<br>INA input has a TTL/CMOS compatible input threshold. This pin is pulled low internally if left open. It<br>is recommended to tie this pin to ground if not used to achieve better noise immunity.                                                                                                                                        |

| INB     | 2          | 2          | Input signal for B channel.<br>INB input has a TTL/CMOS compatible input threshold. This pin is pulled low internally if left open. It<br>is recommended to tie this pin to ground if not used to achieve better noise immunity.                                                                                                                                        |

| VCCI    | 3,8        | 3,8        | Primary-side supply voltage.<br>Locally decoupled to GND using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                      |

| GND     | 4          | 4          | Primary-side ground reference.<br>All signals in the primary side are referenced to this ground.                                                                                                                                                                                                                                                                        |

| DISABLE | 5          | 5          | Disables both driver outputs if asserted high, enables if set low or left open.<br>This pin is pulled low internally if left open. If this pin is not used, it is recommended to ground this pin<br>to obtain better noise immunity. When connecting to a microcontroller, use a low ESR/ESL capacitor<br>of approximately 1nF to bypass the DIS pin.                   |

| DT      | 6          | 6          | Programmable dead time function.<br>Tying DT to VCCI allows the outputs to overlap. Leaving DT open sets, the dead time to <15 ns. Placing<br>a 500- $\Omega$ to 500-k $\Omega$ resistor (RDT) between DT and GND adjusts dead time according to: DT (in ns) $\approx$<br>10 x R <sub>DT</sub> (in k $\Omega$ ). It is not recommended to parallel a ceramic capacitor. |

| NC      | 7,12,13    | 7          | No Internal connection.                                                                                                                                                                                                                                                                                                                                                 |

| VSSB    | 9          | 9          | Ground for secondary-side driver B.<br>Ground reference for secondary side B channel.                                                                                                                                                                                                                                                                                   |

| OUTB    | 10         | 10         | Output of driver B.<br>Connect to the gate of the B channel FET or IGBT.                                                                                                                                                                                                                                                                                                |

| VDDB    | 11         | 11         | Secondary-side power for driver B.<br>Locally decoupled to VSSB using low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                                 |

| VSSA    | 14         | 14         | Ground for secondary-side driver A.<br>Ground reference for secondary side A channel.                                                                                                                                                                                                                                                                                   |

| OUTA    | 15         | 15         | Output of driver A.<br>Connect to the gate of the A channel FET or IGBT.                                                                                                                                                                                                                                                                                                |

| VDDA    | 16         | 16         | Secondary-side power for driver A.<br>Locally decoupled to VSSA using a low ESR/ESL capacitor located as close to the device as possible.                                                                                                                                                                                                                               |

## **2. Specifications** 2.1.Absolute Maximum Ratings

Table 2. Absolute Maximum Ratings (1)

| PARAMETER                                  | SYMBOL                                              | MIN                          | MAX                | UNIT |

|--------------------------------------------|-----------------------------------------------------|------------------------------|--------------------|------|

| Input power supply voltage                 | VCCI to GND                                         | -0.6                         | 7                  | V    |

| Driver bias supply                         | VDDA-VSSA, VDDB-VSSB                                | VDDA-VSSA, VDDB-VSSB –0.4 30 |                    | V    |

| Input signal voltage                       | INA, INB, DIS, DT to GND                            | -0.6                         | VCCI+0.5           | V    |

| Input signal voltage                       | INA, INB Transient for 50ns                         | -5                           | VCCI+0.5           | V    |

| Output signal voltage                      | OUTA to VSSA, OUTB to VSSB                          | -0.4                         | VDDA+0.5, VDDB+0.5 | V    |

| Output signal voltage                      | OUTA to VSSA, OUTB to VSSB,<br>Transient for 200 ns | -2                           | VDDA+0.5, VDDB+0.5 | v    |

| Channel to channel voltage                 | VSSA-VSSB, VSSB-VSSA                                | -1500                        | 1500               | V    |

| Junction temperature, $T_J$ <sup>(2)</sup> | Тյ                                                  | -40                          | 150                | °C   |

| Storage temperature, T <sub>stg</sub>      | T <sub>stg</sub>                                    | -65                          | 150                | °C   |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

2) To maintain the recommended operating conditions for TJ, see the Thermal Information.

#### 2.2.ESD Caution

#### ESD(Electrostatic Discharge) Sensitive device

Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### 2.3. Recommended Operating Conditions

Table 3. Over operating free-air temperature range (unless otherwise noted)

| SYMBOL                              | DESCRIPTION                                 | MIN   | MAX              | UNIT |

|-------------------------------------|---------------------------------------------|-------|------------------|------|

| VCCI                                | VCCI Input supply voltage                   | 3     | 5.5              | V    |

|                                     | Pai8232B/Pai8233B Driver output bias supply | 6.5   | 25               | V    |

| VDDA-VSSA, VDDB-VSSB                | Pai8232C/Pai8233C Driver output bias supply | 9.2   | 25               |      |

| VIA-GND, VIB-GND, DISABLE-<br>GND,  | Input voltage                               | 0     | V <sub>CCI</sub> | V    |

| VOA-VSSA, VOB-VSSB                  | Output voltage                              | 0     | VDDA/VDDB        | V    |

| VSSA-VSSB/VSSA-GND/VSSB-GND         | Channel to channel working voltage          | -1200 | 1200             | V    |

| t <sub>INA</sub> , t <sub>INB</sub> | Valid pulse width                           | 10    | /                | ns   |

| T <sub>A</sub>                      | Ambient Temperature under Bias              | -40   | 125              | °C   |

| Tj                                  | Junction Temperature                        | -40   | 130              | °C   |

## 2.4.Thermal Information

Table 4. Thermal Information

|  | SYMBOL           | PARAMETER                              | TYF        | UNIT       |      |

|--|------------------|----------------------------------------|------------|------------|------|

|  |                  | PARAIVIETER                            | NB SOIC-16 | WB SOIC-14 | UNIT |

|  | R <sub>0JA</sub> | Junction-to-ambient thermal resistance | 105        | 101        | °C/W |

## 2.5. Power Ratings

Table 5. Thermal Information

VCCI = 3.3 V, VDDA/B = 12 V, INA/B = 3.3 V, 2MHz 50% duty cycle square wave 1nF load

| SYMBOL   | PARAMETER                             | VAI        | UNIT       |      |

|----------|---------------------------------------|------------|------------|------|

| STIVIBUL | PARAIVIETER                           | NB SOIC-16 | WB SOIC-14 | UNIT |

| PD       | Power dissipation                     | 0.703      | 0.703      | w    |

| PDI      | Power dissipation by transmitter side | 0.003      | 0.003      | w    |

| PDA, PDB | Power dissipation by each driver side | 0.35       | 0.35       | w    |

# 3. Insulation Specifications

Table 6.Insulation Specifications

| PARAMETER           | DESCRIPTION                    | TEST CONDITIONS                                                                     | VA         | UNIT                                                                                    |      |

|---------------------|--------------------------------|-------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------|------|

| PARAIVIETER         | DESCRIPTION                    | TEST CONDITIONS                                                                     | NB SOIC-16 | WB SOIC-14        >8        >8        >21        >400        II        I-IV        I-IV | UNIT |

| CLR                 | External clearance             | Shortest pin-to-pin distance through air                                            | > 4        | > 8                                                                                     | mm   |

| CPG                 | External creepage              | Shortest pin-to-pin distance across the package surface                             | > 4        | > 8                                                                                     | mm   |

| DTI                 | Distance through<br>insulation | Minimum internal gap (internal clearance)<br>of the double insulation (2 × 10.5 µm) | >21        | >21                                                                                     | μm   |

| СТІ                 | Comparative tracking index     | DIN EN 60112 (VDE 0303-11); IEC 60112                                               | > 400      | > 400                                                                                   | V    |

| Material group      | Material group                 | According to IEC 60664-1                                                            | П          | П                                                                                       |      |

|                     |                                | Rated mains voltage ≤150 VRMS                                                       | I-IV       | I-IV                                                                                    |      |

|                     |                                | Rated mains voltage ≤ 300 VRMS                                                      | 1-111      | I-IV                                                                                    |      |

| Overvoltage categor | y per IEC 60664-1              | Rated mains voltage ≤ 600 VRMS                                                      | 1-11       | I-IV                                                                                    |      |

|                     |                                | Rated mains voltage ≤ 1000 VRMS                                                     | /          | 1-111                                                                                   |      |

Table 7. DIN EN IEC 60747-17 (VDE 0884-17):2021-10

| PARAMETER         | DESCRIPTION                                  | TEST CONDITIONS                                                                                                          | VA         | UNIT       |                  |

|-------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------|------------|------------------|

|                   | DESCRIPTION                                  |                                                                                                                          | NB SOIC-16 | WB SOIC-14 |                  |

| V <sub>IORM</sub> | Maximum repetitive<br>peak isolation voltage | AC voltage (bipolar)                                                                                                     | 1200       | 1200       | V <sub>PK</sub>  |

| M                 | Maximum working isolation voltage            | AC voltage (sine wave)                                                                                                   | 848        | 848        | V <sub>RMS</sub> |

| V <sub>IOWM</sub> |                                              | DC voltage                                                                                                               | 1200       | 1200       | V <sub>DC</sub>  |

| VIOTM             | Maximum transient isolation voltage          | $V_{TEST} = V_{IOTM}$ , t = 60 sec<br>(qualification)<br>$V_{TEST} = 1.2 \times V_{IOTM}$ , t = 1 s (100%<br>production) | 4242       | 7071       | V <sub>PK</sub>  |

| V <sub>IOSM</sub> | Maximum surge isolation voltage              | Test method per IEC 62368-1,<br>1.2/50 $\mu$ s waveform, V <sub>TEST</sub> = 1.3 ×<br>V <sub>IOSM</sub> (qualification)  | 5000       | 5000       | V <sub>PK</sub>  |

| PARAMETER         | DESCRIPTION                             | TEST CONDITIONS                                                                                                                                                                      | VA                 | LUE                                                                                        | UNIT |

|-------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------------------------------------------------------|------|

| FARAIVIETER       | DESCRIPTION                             | TEST CONDITIONS                                                                                                                                                                      | NB SOIC-16         | ALUE      WB SOIC-14      <5      <5      <5      <5      1.2      > $10^{12}$ > $10^{11}$ |      |

|                   |                                         | Method a, After Input/Output<br>safety test subgroup 2/3.<br>$V_{ini} = V_{IOTM}$ , $t_{ini} = 60s; V_{pd(m)} = 1.2 X$<br>$V_{IORM}$ , $t_m = 10s$                                   | <5                 | <5                                                                                         | рC   |

| q <sub>pd</sub>   | Apparent charge                         | Method a, After environmental<br>tests subgroup $1.V_{ini} = V_{IOTM}$ , $t_{ini} = 60s; V_{pd(m)} = 1.3 X V_{IORM}$ , $t_m = 10s$                                                   | <5                 | <5                                                                                         | pC   |

|                   |                                         | Method b1; At routine test<br>(100% production) and<br>preconditioning (type test)<br>$V_{ini} = 1.2 \times V_{IOTM}$ ; $t_{ini} = 1s; V_{pd(m)} =$<br>1.5 * $V_{IORM}$ , $t_m = 1s$ | <5                 | <5                                                                                         | pC   |

| C <sub>IO</sub>   | Barrier capacitance,<br>input to output | V <sub>IO</sub> = 0.4 sin (2πft), f =1 MHz                                                                                                                                           | 1.2                | 1.2                                                                                        | pF   |

|                   |                                         | V <sub>IO</sub> = 500 V at T <sub>A</sub> = 25°C                                                                                                                                     | > 10 <sup>12</sup> | > 10 <sup>12</sup>                                                                         | Ω    |

| R <sub>IO</sub>   | Isolation resistance,                   | $V_{IO}$ = 500 V at 100°C $\leq$ T <sub>A</sub> $\leq$ 125°C                                                                                                                         | > 10 <sup>11</sup> | > 10 <sup>11</sup>                                                                         | Ω    |

|                   | input to output                         | V <sub>IO</sub> = 500 V at T <sub>S</sub> =150°C                                                                                                                                     | > 109              | > 109                                                                                      | Ω    |

| Pollution degree  |                                         |                                                                                                                                                                                      | 2                  | 2                                                                                          |      |

| Climatic category |                                         |                                                                                                                                                                                      | 40/125/21          | 40/125/21                                                                                  |      |

#### Table 8.UL 1577

| PARAMETER        | DESCRIPTION TEST CONDITIONS |                                                                                                                     | VA         | LINUT      |                  |

|------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------|------------|------------|------------------|

| PARAIVIETER      | DESCRIPTION                 | TEST CONDITIONS                                                                                                     | NB SOIC-16 | WB SOIC-14 | UNIT             |

| V <sub>ISO</sub> | Withstand isolation voltage | $V_{TEST} = V_{ISO}$ , t = 60 sec.(qualification),<br>$V_{TEST} = 1.2 \times V_{ISO}$ , t = 1 sec (100% production) | 3000       | 5000       | V <sub>RMS</sub> |

## 3.1.Safety-Related Certifications

| REGULATORY | NB SOIC-16                                                                                                                                                                                                                | WB SOIC-14                                                                                                                                                               |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CQC        | Certified according to GB 4943.1-2022<br>Reinforced Insulation, Altitude $\leq$ 5000 m, Tropical<br>Climate 660 V <sub>RMS</sub> maximum working voltage.<br>File (Pending)                                               | Certified according to GB 4943.1-2022<br>Reinforced Insulation, Altitude $\leq$ 5000 m, Tropical Climate 660 V <sub>RMS</sub> maximum working voltage.<br>File (Pending) |

| UL         | Recognized under UL 1577 Component Recognition<br>Program<br>Single protection, 3000V <sub>RMS</sub><br>File: UL-US-L494497-11-52017102-10                                                                                | Recognized under UL 1577 Component Recognition<br>Program<br>Single protection, 5000V <sub>RMS</sub><br>File: UL-US-L494497-11-52017102-10                               |

| VDE        | $\begin{array}{l} \mbox{Certified according to DIN EN IEC 60747-17 (VDE 0884-17) :2021-10,and EN IEC 60747-17: 2020+AC: 2021 \\ \mbox{V}_{IOTM} = \!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | $\begin{array}{l} Certified according to DIN EN IEC 60747-17 (VDE 0884-17) :2021-10,and EN IEC 60747-17: 2020+AC: 2021 $$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$$               |

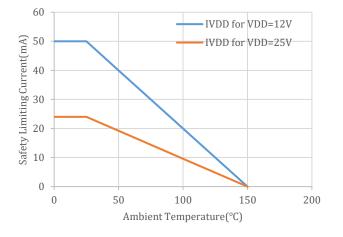

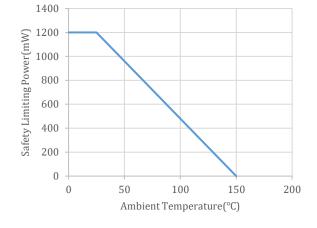

### 3.2.Safety-Limiting Values

Safety limiting intends to minimize potential damage to the isolation barrier upon failure of input or output circuitry.

Table 10.Safety-Limiting Values

| SYMBOL   | PARAMETER                  | TEST CONDITIONS                                                            | SIDE     | MAX        |            | UNIT  |

|----------|----------------------------|----------------------------------------------------------------------------|----------|------------|------------|-------|

| STIVIBOL | PARAIVIETER                | TEST CONDITIONS                                                            | SIDE     | NB SOIC-16 | WB SOIC-14 | UNIT  |

|          | Safety output<br>Is supply | $R_{\theta JA}$ = 101 °C/W, VDDA/B = 12 V, $T_A$ =                         | Driver A | 50         | 50         | mA    |

| L.       |                            | 25°C, T」= 150°C                                                            | Driver B | 50         | 50         | ША    |

| IS       | current                    | $R_{\theta JA} = 101 \degree C/W$ , VDDA/B = 25 V, $T_A =$                 | Driver A | 24         | 24         | m (   |

|          | current                    | 25°C, T₁ = 150°C                                                           | Driver B | 24         | 24         | mA    |

| D.       | Safety supply              | R <sub>θJA</sub> = 101°C/W, T <sub>A</sub> = 25°C, T <sub>J</sub> = 150°C  | TOTAL    | 1200       | 1200       | mW    |

| Ps       | power                      | $R_{\theta JA} = 101 \text{ C/W}, T_A = 23 \text{ C}, T_J = 130 \text{ C}$ | TOTAL    | 1200       | 1200       | IIIVV |

| т        | Safety                     |                                                                            |          | 150        | 150        | °C    |

| Ts       | temperature <sup>1</sup>   |                                                                            |          | 130        | 130        | Ľ     |

The maximum safety temperature, T<sub>s</sub>, has the same value as the maximum junction temperature, T<sub>J</sub>, specified for the device. The I<sub>s</sub> and P<sub>s</sub> parameters represent the safety current and safety power respectively. The maximum limits of I<sub>s</sub> and P<sub>s</sub> should not be exceeded. These limits vary with the ambient temperature, T<sub>A</sub>.

The junction-to-air thermal resistance,  $R_{\theta JA}$ , in the Thermal Information table is that of a device installed on a high-K test board for leaded surface-mount packages. Use these equations to calculate the value for each parameter:

$T_J = T_A + R_{\theta JA} \times P$ , where P is the power dissipated in the device.

$T_{J(max)} = T_S = T_A + R_{\theta JA} \times P_S$ , where  $T_{J(max)}$  is the maximum allowed junction temperature.  $P_S = I_S \times V_I$ , where  $V_I$  is the maximum input voltage.

## 4. Truth table

Table 11.Truth table

| INF | νUT |                   | VCCI/V    | /DDA/VDDB Con          | dition                 | ουτ            | PUT            | NOTES                                                                                       |  |

|-----|-----|-------------------|-----------|------------------------|------------------------|----------------|----------------|---------------------------------------------------------------------------------------------|--|

| INA | INB | DISABLE           | VCCI      | VDDA                   | VDDB                   | VOA            | VOB            | NOTES                                                                                       |  |

| L   | L   | L or Left<br>Open | Powered   | Powered                | Powered                | L              | L              | If Dead Time function is used,                                                              |  |

| L   | Н   | L or Left<br>Open | Powered   | Powered /<br>Unpowered | Powered                | L              | H <sup>2</sup> | output transitions occur after<br>the dead time expires. See<br>Programmable Dead Time (DT) |  |

| н   | L   | L or Left<br>Open | Powered   | Powered                | Powered /<br>Unpowered | H <sup>2</sup> | L              | Pin <sup>2</sup>                                                                            |  |

| н   | Н   | L or Left<br>Open | Powered   | Powered                | Powered                | L              | L              | DT is left open or programmed with $R_{\text{DT}}$                                          |  |

| Н   | Н   | L or Left<br>Open | Powered   | Powered                | Powered                | H <sup>2</sup> | H <sup>2</sup> | DT pin pulled to VCCI.                                                                      |  |

| X1  | X1  | Н                 | Powered   | Powered                | Powered                | L              | L              |                                                                                             |  |

| L   | L   | L or Left<br>Open | Unpowered | Powered                | Powered                | L              | L              |                                                                                             |  |

Notes:

1) "X" means L, H or left open.

2) The VOA/VOB output is high only in this case. If there are other conditions, VOA / VOB output is low.

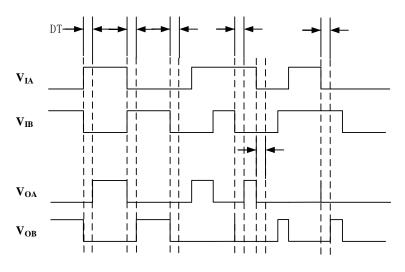

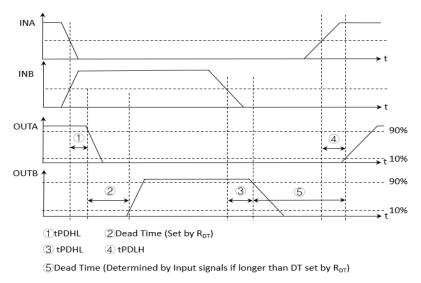

$T_{DT} \approx 10^{*} R_{DT}$  ( $T_{DT}$  is in nS and  $R_{DT}$  is in k $\Omega$ ).Connect DT to VCCI to overlap the output. Keep DT open to set the dead time to <15ns.Place a 500 $\Omega$  to 500k $\Omega$  resistor ( $R_{DT}$ ) between DT and GND to adjust the dead time according to the following conditions: DT(ns)  $\approx 10 \times R_{DT}(k\Omega)$ .

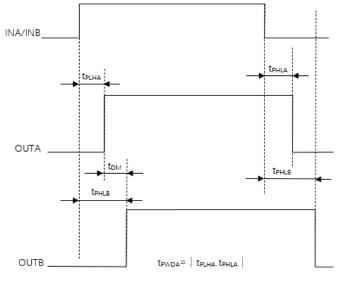

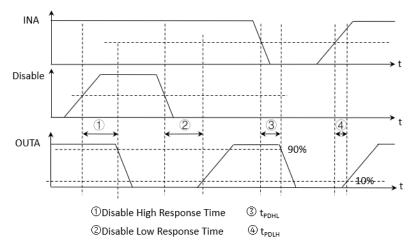

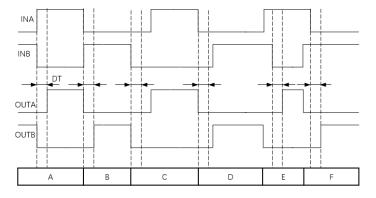

Fig 3.Input/Output Timing Diagram

# 5. Specifications

## 5.1. Electrical Characteristics

Table 12.ELECTRICAL CHARACTERISTICS

VCCI = 3.3 V or 5 V, 0.1- $\mu$ F capacitor from VCCI to GND, VDDA = VDDB = 12 V, 1- $\mu$ F capacitor from VDDA and VDDB to VSSA and VSSB, T<sub>A</sub> = -40 to +125°C, (unless otherwise noted)

| PARAMETER                                                             | DESCRIPTION                                 | TEST CONDITIONS                                                                                                  | MIN  | ТҮР | ΜΑΧ  | UNIT |

|-----------------------------------------------------------------------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| I <sub>VCCI</sub>                                                     | VCCI quiescent current                      | V <sub>INA</sub> = 0 V, V <sub>INB</sub> = 0 V                                                                   |      | 0.5 | 1.1  | mA   |

| I <sub>VDDA</sub> , I <sub>VDDB</sub>                                 | VDDA and VDDB quiescent current             | V <sub>INA</sub> = 0 V, V <sub>INB</sub> = 0 V                                                                   |      | 0.9 | 1.5  | mA   |

| Ivcci                                                                 | VCCI operating current                      | VINA, VINB input signal f = 500 kHz,<br>50% duty cycle, each channel load<br>capacitance 100 pF ± 20%, including |      | 0.9 |      | mA   |

| I <sub>vdda</sub> , I <sub>vddb</sub>                                 | VDDA and VDDB operating current             | the input capacitance of the measuring instrument.                                                               |      | 2.2 |      | mA   |

| V <sub>VCCI_ON</sub>                                                  | VCCI UVLO Rising threshold                  |                                                                                                                  | 2.55 | 2.7 | 2.85 | V    |

| Vvcci_off                                                             | VCCI UVLO Falling threshold                 |                                                                                                                  | 2.35 | 2.5 | 2.65 | V    |

| V <sub>VCCI_HYS</sub>                                                 | UVLO Threshold hysteresis                   |                                                                                                                  |      | 0.2 |      | V    |

| V <sub>VDDA_ON</sub> ,<br>V <sub>VDDB_ON</sub>                        | Pai8232C/Pai8233C UVLO Rising threshold     |                                                                                                                  | 8.3  | 8.7 | 9.2  | v    |

| Vvdda_off,<br>Vvddb_off                                               | Pai8232C/Pai8233C UVLO Falling threshold    |                                                                                                                  | 7.8  | 8.2 | 8.7  | v    |

| V <sub>VDDA_HYS</sub><br>V <sub>VDDB_HYS</sub>                        | Pai8232C/Pai8233C UVLO Threshold hysteresis |                                                                                                                  |      | 0.5 |      | v    |

| Vvdda_on,<br>Vvddb_on                                                 | Pai8232B/Pai8233B UVLO Rising threshold     |                                                                                                                  | 5.7  | 6.1 | 6.5  | v    |

| Vvdda_off,<br>Vvddb_off                                               | Pai8232B/Pai8233B UVLO Falling threshold    |                                                                                                                  | 5.4  | 5.8 | 6.2  | v    |

| V <sub>VDDA_HYS</sub><br>Vvddb_hys                                    | Pai8232B/Pai8233B UVLO Threshold hysteresis |                                                                                                                  |      | 0.3 |      | v    |

| VINAH, VINBH, VDISH                                                   | Input high threshold voltage                |                                                                                                                  | 1.6  | 1.8 | 2    | V    |

| VINAL, VINBL, VDISL                                                   | Input low threshold voltage                 |                                                                                                                  | 0.8  | 1   | 1.2  | V    |

| V <sub>INA_HYS</sub> , V <sub>INB_HYS</sub> ,<br>V <sub>DIS_HYS</sub> | Input threshold hysteresis                  |                                                                                                                  |      | 0.8 |      | V    |

| PARAMETER                           | DESCRIPTION                                 | TEST CONDITIONS                                                                                                                                                                         | MIN     | ТҮР              | МАХ      | UNIT |

|-------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------------------|----------|------|

| VINA, VINB                          | Negative transient, ref to GND, 50ns pulse  | Not production tested, bench test<br>only                                                                                                                                               | -5      |                  |          | v    |

|                                     | Pai8233B/C Peak output source current       |                                                                                                                                                                                         |         | 4                |          | ^    |

| I <sub>OA+</sub> , I <sub>OB+</sub> | Pai8232B/C Peak output source current       | C <sub>VDD</sub> = 10 μF, C <sub>LOAD</sub> = 0.68 μF, f=                                                                                                                               |         | 2                |          | A    |

|                                     | Pai8233B/C Peak output sink current         | 100Hz, bench measurement                                                                                                                                                                |         | 8                |          | •    |

| Ioa-, Iob-                          | Pai8232B/C Peak output sink current         |                                                                                                                                                                                         |         | 4                |          | A    |

| Rона, Rонв                          | Output resistance at high state             | $I_{OUT} = -10$ mA, TA = 25°C, $R_{OHA}$ ,<br>$R_{OHB}$ do not represent drive pull- up<br>performance. See $t_{RISE}$ in Switching<br>Characteristics and Output Stage for<br>details. |         | 1                |          | Ω    |

| R <sub>ola</sub> , R <sub>olb</sub> | Output resistance at low state              | I <sub>OUT</sub> = 10 mA, TA = 25°C                                                                                                                                                     |         | 0.4              |          | Ω    |

| Voha, Vohb                          | Output voltage at high state                | VDDA, VDDB = 12 V, IOUT = -10 mA,<br>TA = 25°C                                                                                                                                          |         | 11.99            |          | v    |

| $V_{\text{OLA}}, V_{\text{OLB}}$    | Output voltage at low state                 | VDDA, VDDB = 12 V, IOUT = 10 mA,<br>TA = 25°C                                                                                                                                           |         | 4                |          | mV   |

|                                     |                                             | Pull DT pin to VCCI                                                                                                                                                                     | Overlap | determine<br>INB | d by INA | ns   |

| DT                                  | Dead time                                   | DT pin is left open, min spec<br>characterized only, tested for<br>outliers                                                                                                             | 0       | 8                | 15       | ns   |

|                                     |                                             | R <sub>DT</sub> = 20 kΩ                                                                                                                                                                 | 150     | 200              | 250      | ns   |

| T <sub>JF</sub>                     | Junction Temperature Shutdown, Falling Edge |                                                                                                                                                                                         |         | 140              |          | °C   |

| T <sub>JR</sub>                     | Junction Temperature Shutdown, Rising Edge  |                                                                                                                                                                                         |         | 150              |          | °C   |

#### 5.2. Switching Characteristics

Table 13.Switching Characteristics

VCCI = 3.3 V or 5 V, 0.1- $\mu$ F capacitor from VCCI to GND, VDDA = VDDB = 12 V, 1- $\mu$ F capacitor from VDDA and VDDB to VSSA and VSSB, no load, TA = -40°C to +125°C, (unless otherwise noted).

| PARAMETER          | DESCRIPTION                                                   | TEST CONDITIONS                                     | MIN | ТҮР | MAX | UNIT  |

|--------------------|---------------------------------------------------------------|-----------------------------------------------------|-----|-----|-----|-------|

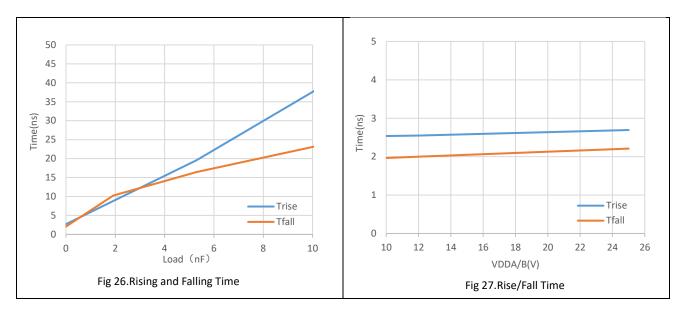

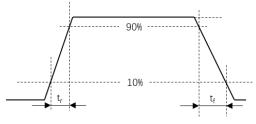

| tr                 | Output rise time                                              | C <sub>OUT</sub> = 1.8 nF                           |     | 7   | 18  | ns    |

| t <sub>f</sub>     | Output fall time                                              | C <sub>OUT</sub> = 1.8 nF                           |     | 8   | 12  | ns    |

| t <sub>PWmin</sub> | Minimum pulse width                                           | Output off for less than minimum, Cout<br>= 0 pF    |     | 10  | 20  | ns    |

| t <sub>PDHL</sub>  | Propagation delay from INx to OUTx falling edges              |                                                     | 14  | 19  | 30  | ns    |

| tpdlh              | Propagation delay from INx to OUTx rising edges               |                                                     | 14  | 19  | 30  | ns    |

| tpwd               | Pulse width distortion  t <sub>PDLH</sub> – t <sub>PDHL</sub> |                                                     |     |     | 5   | ns    |

| t <sub>DM</sub>    | Propagation delays matching<br>between VOUTA, VOUTB           | f = 100 kHz                                         |     |     | 5   | ns    |

| CM <sub>H</sub>    | High-level common-mode<br>transient immunity                  | INA and INB both are tied to VCCI; $V_{CM}$ =1000V; |     | 100 |     | kV/us |

| CML                | Low-level common-mode transient immunity                      | INA and INB both are tied to GND; $V_{CM}$ =1000V;  |     | 100 |     | kV/us |

| t <sub>sD</sub>    | Shutdown Time from Disable<br>True                            |                                                     |     |     | 40  | ns    |

| trestart           | Restart Time from Disable False                               |                                                     |     |     | 40  | ns    |

| tstart             | Device Start-up Time                                          | Time from VDD_=VDD_UV+ to VOA,<br>VOB = VIA, VIB    |     |     | 100 | μs    |

## 5.3. Insulation Characteristics Curves

Fig 4.Thermal Derating Curve for Limiting Current Per VDE

Fig 5.Thermal Derating Curve for Limiting Power Per VDE

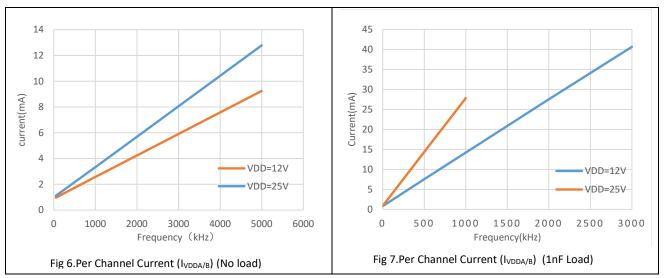

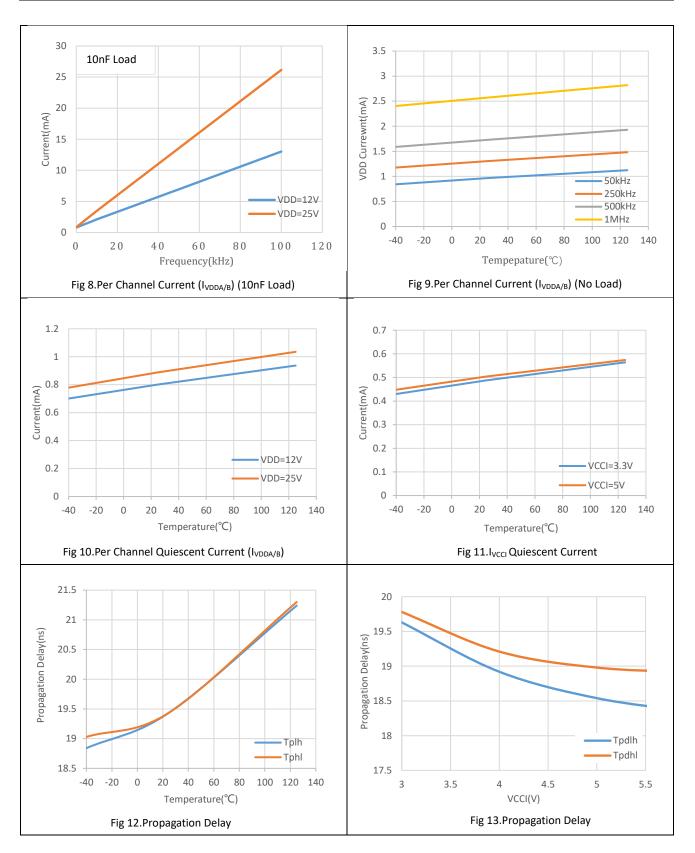

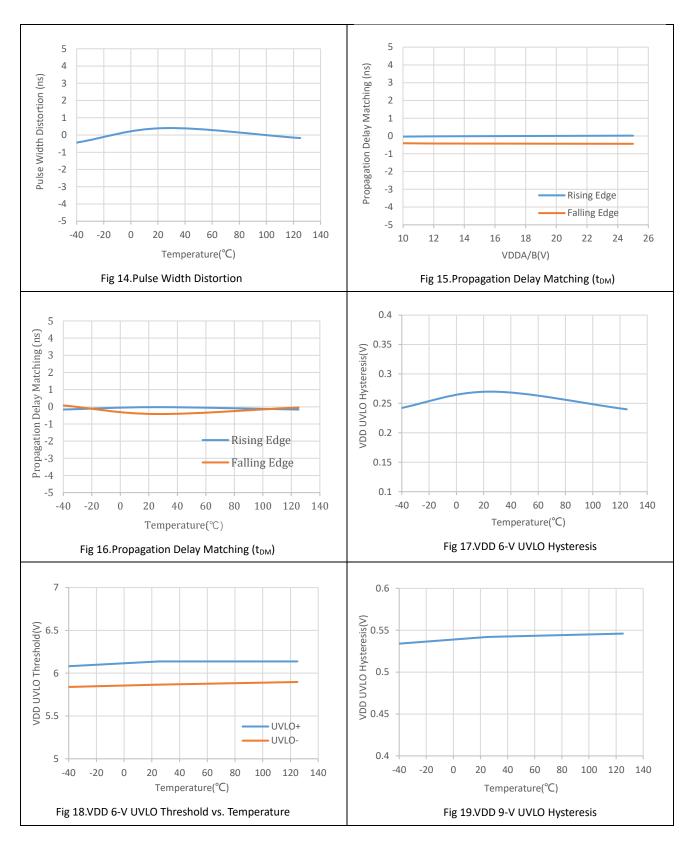

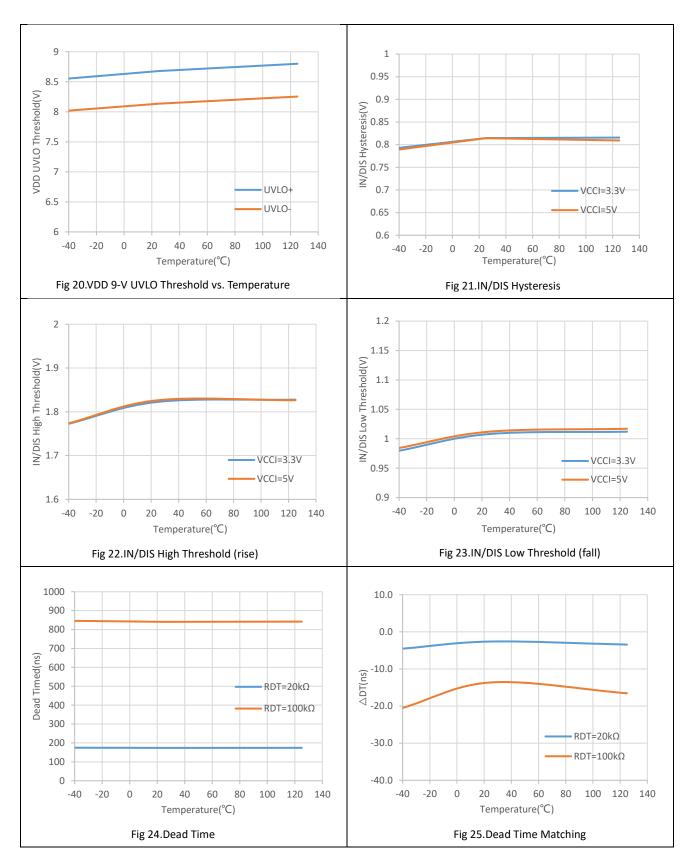

#### 5.4. Typical Characteristics

VDDA = VDDB= 12 V, VCCI = 3.3 V, TA = 25°C, No load, unless otherwise noted.

# 6. Parameter Measurement Information

#### 6.1. Propagation Delay Matching and Pulse Width Distortion

Fig 28 shows how to calculate pulse width distortion( $t_{PWD}$ ) and delay matching ( $t_{DM}$ ) from the propagation delays of channels A and B. It can be measured by ensuring that both inputs are in phase and disabling the dead time function by shorting the DT Pin to VCCI.

Fig 28.Overlapping inputs, Dead Time Disable

#### 6.2. Rising and Falling Time

Fig 29 shows the criteria for measuring rising (t\_r) and falling (t\_f) times.

Fig 29. Rising and Falling Time Criteria

#### 6.3. Input and Disable Response Time

Fig 30 shows the response time of the disable function. It is recommended to bypass using a 1nF low ESR/ESL capacitor close to DIS pin when connecting DIS pin to a micro controller with distance.

Fig 30.Disable Pin Timing

## 6.4. Programable Dead Time

Leaving the DT pin open or tying it to GND through an appropriate resistor (R<sub>DT</sub>) sets a dead-time interval.

Fig 31.Dead Time Switching Parameters

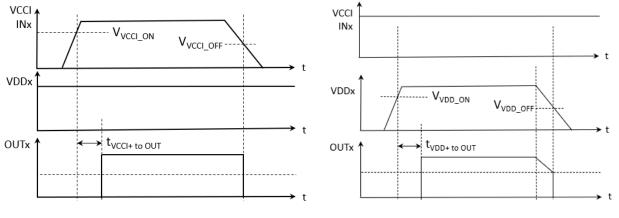

## 6.5. Power-up UVLO Delay to OUTPUT

Before the driver is ready to deliver a proper output state, there is a power-up delay from the UVLO rising edge to output and it is defined as  $t_{VCCI+ to OUT}$  for VCCI UVLO (typically 40us) and  $t_{VDD+ to OUT}$  for VDD UVLO (typically 45us). It is recommended to consider proper margin before launching PWM signal after the driver's VCCI and VDD bias supply is ready. Fig 32 and Fig 33 show the power up UVLO delay timing diagram for VCCI and VDD.

If INA or INB are active before VCCI or VDD have crossed above their respective on thresholds, the output will not update until  $t_{VCCI+to}$ out or  $t_{VDD+to OUT}$  after VCCI or VDD crossing its UVLO rising threshold. However, when either VCCI or VDD receive a voltage less than their respective off thresholds, there is <1 $\mu$ s delay, depending on the voltage slew rate on the supply pins, before the outputs are held low. This asymmetric delay is designed to ensure safe operation during VCCI or VDD brownouts.

Fig 32.VCCI Power-up UVLO Delay

Fig 33.VDDA/B Power-up UVLO Delay

#### 6.6.CMTI Testing

Fig 34 is a simplified diagram of the CMTI test configuration.

Fig 34.Simplified CMTI test setup

# 7. Detailed Description

#### 7.1.Overview

The Pai8232B/C and Pai8233B/C are flexible dual-channel gate drivers. The Pai8232B/C and Pai8233B/C have many functions that can make it well integrated with the control circuit and protect the drove devices, such as programmable dead time (DT) control, DISABLE function and undervoltage lockout (UVLO) function. When the input remains open or the input pulse width is insufficient, Pai8232B/C and Pai8233B/C keeps its output low.

#### 7.2. Feature Description

#### 7.2.1. VDD, VCCI, and Under Voltage Lock Out (UVLO)

The Pai8232B/C and Pai8233B/C have under-voltage protection (UVLO) function in primary and secondary side. When the VDD voltage is lower than  $V_{VDD_ON}$  at device start-up or lower than  $V_{VDD_OFF}$  after start-up, the VDD UVLO feature holds the effected output low, regardless of the status of the input pins (INA and INB).

Table 14.Pai8232B/Cand Pai8233B/C VCCI UVLO Feature Logic

| CONDITION                                                                                         | INPUTS |     | OUTP | UTS  |

|---------------------------------------------------------------------------------------------------|--------|-----|------|------|

| CONDITION                                                                                         | INA    | INB | OUTA | OUTB |

|                                                                                                   | Н      | L   | L    | L    |

| VCCLCND <v device="" during="" start="" td="" up<=""><td>L</td><td>Н</td><td>L</td><td>L</td></v> | L      | Н   | L    | L    |

| VCCI-GND < V <sub>VCCI_ON</sub> during device start up                                            | Н      | Н   | L    | L    |

|                                                                                                   | L      | L   | L    | L    |

|                                                                                                   | Н      | L   | L    | L    |

| VCCLCND < V ofter device start up                                                                 | L      | Н   | L    | L    |

| VCCI-GND < V <sub>VCCI_OFF</sub> after device start up                                            | Н      | Н   | L    | L    |

|                                                                                                   | L      | L   | L    | L    |

Table 15. VDDA/B UVLO Feature Logic

| CONDITION                                                       | INPU | JTS | OUTP | UTS  |

|-----------------------------------------------------------------|------|-----|------|------|

| CONDITION                                                       | INA  | INB | OUTA | OUTB |

|                                                                 | Н    | L   | L    | L    |

| VDDA/D_VSSA/D_cV/during douise start up                         | L    | н   | L    | L    |

| VDDA/B -VSSA/B < $V_{VDD_ON}$ during device start up            | Н    | н   | L    | L    |

|                                                                 | L    | L   | L    | L    |

|                                                                 | Н    | L   | L    | L    |

| VDDA/R_VSSA/R_ </td <td>L</td> <td>н</td> <td>L</td> <td>L</td> | L    | н   | L    | L    |

| VDDA/B -VSSA/B < V <sub>VDD_OFF</sub> after device start up     | Н    | н   | L    | L    |

|                                                                 | L    | L   | L    | L    |

#### 7.2.2. Input and Output Logic Table

Table 16.INPUT/OUTPUT Logic Table (Assume VCCI, VDDA, VDDB are powered up.)

| IN  | PUTS | DICADLE        | OUTPUTS |      | NOTE                                                           |  |

|-----|------|----------------|---------|------|----------------------------------------------------------------|--|

| INA | INB  | DISABLE        | OUTA    | OUTB | ΝΟΤΕ                                                           |  |

| L   | L    | L or Left Open | L       | L    | If Dead Time function is used, output transitions              |  |

| L   | Н    | L or Left Open | L       | Н    | occur after the dead time expires.                             |  |

| Н   | L    | L or Left Open | Н       | L    |                                                                |  |

| Н   | Н    | L or Left Open | L       | L    | DT is left open or programmed with $R_{\mbox{\scriptsize DT}}$ |  |

| Н         | Н         | L or Left Open | Н | Н | DT pin pulled to VCCI |

|-----------|-----------|----------------|---|---|-----------------------|

| Left Open | Left Open | L or Left Open | L | L | -                     |

| X1        | X1        | Н              | L | L | -                     |

(1) "X" means L, H or left open.

#### 7.3.Disable Function

Setting the DISABLE pin high shuts down both outputs simultaneously. Grounding (or left open) the DISABLE pin allows the Pai8232B/C and Pai8233B/C to operate normally. The DISABLE response time is in the range of 20ns and quite responsive, which is as fast as propagation delay. The DISABLE pin is only functional (and necessary) when VCCI stays above the UVLO threshold. It is recommended to tie this pin to ground if the DISABLE pin is not used to achieve better noise immunity, and it is recommended to bypass using a  $\approx$ 1nF low ESR/ESL capacitor close to DIS pin when connecting DIS pin to a micro controller with distance.

#### 7.4. Programmable Dead Time (DT) Function

The Pai8232B/C and Pai8233B/C allows the user to adjust dead time (DT) in the following ways:

#### 7.4.1. Tying the DT Pin to VCC

Outputs completely match inputs, so no dead time is asserted. This allows outputs to overlap.

#### 7.4.2. DT Pin Left Open or Connected to a Programming Resistor between DT and GND Pins

If the DT pin is left open, the dead time duration ( $t_{DT}$ ) is set to <15 ns. One can program  $t_{DT}$  by placing a resistor,  $R_{DT}$ , between the DT pin and GND. The appropriate  $R_{DT}$  value can be determined from Equation 1, where  $R_{DT}$  is in k $\Omega$  and  $t_{DT}$  is in ns.

$t_{DT} \approx 10 \times R_{DT}$

(1)

An input signal's falling edge activates the programmed dead time for the other signal. The output signals' dead time is always set to the longer of either the driver's programmed dead time or the input signal's own dead time. If both inputs are high simultaneously, both outputs will immediately be set low. This feature is used to prevent shoot-through, and it doesn't affect the programmed dead time setting for normal operation. Various driver dead time logic operating conditions are illustrated and explained in Fig 35.

Table 17. Input and Output Logic Relationship With Input Signals

| CONDITION            | INB       | INA       | OUTPUT                                                                                                                                                                                                                                                                 |  |  |

|----------------------|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| A goes low goes high |           | goes high | INB sets OUTB low immediately and assigns the programmed dead time to OUTA. OUTA is allowed to go high after the programmed dead time.                                                                                                                                 |  |  |

| В                    | goes high | goes low  | Now INA sets OUTA low immediately and assigns the programmed dead time to OUTB.<br>OUTB is allowed to go high after the programmed dead time.                                                                                                                          |  |  |

| С                    | goes low  | still low | Condition C: INB goes low, INA is still lowing sets OUTB low immediately and assigns the programmed dead time for Obtain this case, the input signal's own dead time is longer than the programmed dead time. Thus, when INA goes high, it immediately sets OUTA high. |  |  |

| D | still low  | goes low   | Condition D: INA goes low, INB is still lowing sets OUTA low immediately and assigns the programmed dead time to OUTB.INB's own dead time is longer than the programmed dead time. Thus, when INB goes high, it immediately sets OUTB high.                                                       |

|---|------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E | still high | goes high  | Condition E: INA goes high, while INB and OUTB are still high. To avoid overshoot, INA immediately pulls OUTB low and keeps OUTA low. After some time INB goes low and assigns the programmed dead time to OUTA. OUTB is already low. After the programmed dead time, OUTA is allowed to go high. |

| F | goes high  | still high | Condition F: INB goes high, while INA and OUTA are still high. To avoid overshoot, INB immediately pulls OUTA low and keeps OUTB low. After some time INA goes low and assigns the programmed dead time to OUTB.OUTA is already low. After the programmed dead time, OUTB is allowed to go high.  |

# 8. Typical Application

Note: The information in this section is for reference only, and 2Pai Semi does not guarantee its accuracy or completeness.

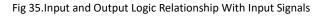

Solution with bootstrap circuits on secondary side and without negative shutdown voltage Fig 36 shows a reference design in which the Pai8232B/C andPai8233B/C is set as a typical half-bridge drive configuration. In this design, only one independent power supply is required on the secondary side, but there is no negative voltage shutdown feature. This solution is suitable for small and medium power scenarios.

Fig 36.Solution with bootstrap circuits on secondary side and without negative shutdown voltage

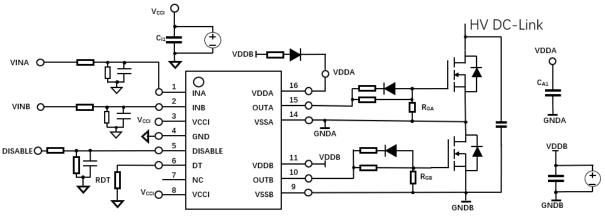

8.1.Enhance anti-interference ability solutions with Single power supply and bootstrap circuits for the secondary side

Fig 37.Enhance anti-interference ability solutions with Single power supply and bootstrap circuits for the secondary side

The solution shows in Fig 37 is an improved solution. Only one independent power supply is needed on the secondary side. By adding a Zener diode in the gate drive loop to construct a negative turn-off voltage, the anti-interference ability of the gate is enhanced. This solution has the following limitations:

1) The negative gate bias is not only determined by the Zener diode, but also depends on the duty cycle, which means that when the negative bias duty cycle changes, the negative turn-off voltage will also change.

2) The high side VDDA-VSSA must maintain enough voltage to stay in the recommended power supply range, which means that the low-side switch must be turned on for enough time in each switching cycle.

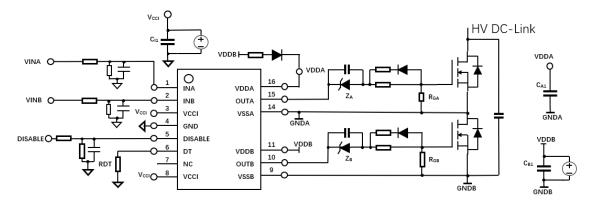

# 8.2. Solution with two independent power supplies on the secondary side and a negative turn-off voltage constructed through the Zener diode

When parasitic inductances are introduced by non-ideal PCB layout and long package leads, there would be ringing in the gate-source drive voltage of the power transistor during high di/dt and dv/dt switching. If the ringing is over the threshold voltage, there is the risk of unintended turn-on and even shoot-through. Applying a negative bias on the gate drive is a popular way to keep such ringing below the threshold. Below are a few examples of implementing negative gate drive bias.

Fig 38 shows the example with negative bias turn-off on the channel A driver using a Zener diode on the isolated power supply output stage. The negative bias is set by the Zener diode voltage. If the isolated power supply VA is equal to 25 V, the turn-off voltage will be - 5.1 V and turn-on voltage will be 20 V.

The channel-B driver circuit is the same as channel-A, therefore, this configuration needs two power supplies for a half-bridge configuration.

Fig 38.Negative Bias with Zener Diode on Iso-Bias Power Supply Output

# 8.3.Solution with two independent/four-way power supplies on the secondary side and a negative shutdown voltage

Fig 39 shows a solution with two independent power supplies on the secondary side and a negative turn-off voltage.

Fig 39.Negative Bias with Two Iso-Bias Power Supplies

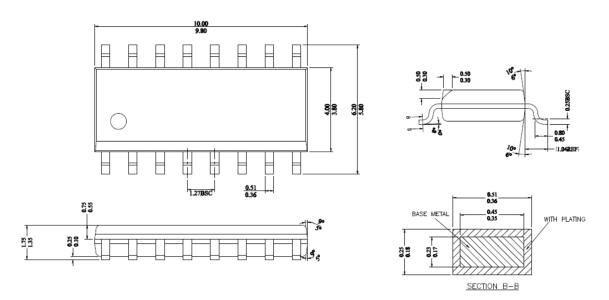

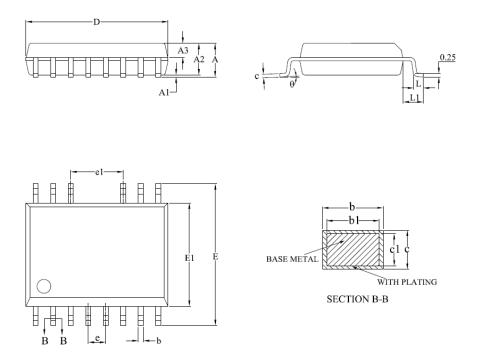

# 9. Outline Dimensions

| SYMBOL | MI      | LLIMET  | ER    |  |  |

|--------|---------|---------|-------|--|--|

| STMBOL | MIN     | NOM     | MAX   |  |  |

| А      | _       | _       | 2.65  |  |  |

| A1     | 0.10    |         | 0.30  |  |  |

| A2     | 2.25    | 2.30    | 2.35  |  |  |

| A3     | 0.97    | 1.02    | 1.07  |  |  |

| b      | 0.35    |         | 0.43  |  |  |

| b1     | 0.34    | 0.37    | 0.40  |  |  |

| с      | 0.25    | _       | 0.29  |  |  |

| c1     | 0.24    | 0.25    | 0.26  |  |  |

| D      | 10.20   | 10.30   | 10.40 |  |  |

| Е      | 10.10   | 10.30   | 10.50 |  |  |

| E1     | 7.40    | 7.50    | 7.60  |  |  |

| е      | 1.27BSC |         |       |  |  |

| e1     | :       | 3.81BSC | 2     |  |  |

| L      | 0.55    | _       | 0.85  |  |  |

| L1     | 1.40REF |         |       |  |  |

| θ      | 0       | _       | 8°    |  |  |

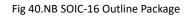

#### Fig 41.WB SOIC-14 Outline Package

#### **10.Land Patterns**

The Fig 41 illustrates the recommended land pattern details for the Pai823xB/C in a 16-pin Narrow body SOIC package. The table lists the values for the dimensions shown in the illustration.

Fig 41.16-Lead Narrow Body SOIC [NB SOIC-16] Land Pattern

Table 18.16-Lead Narrow Body SOIC [NB SOIC-16] Land Pattern Dimensions

| DIMENSION | FEATURE            | PARAMETER | UNIT |

|-----------|--------------------|-----------|------|

| C1        | Pad column spacing | 5.40      | mm   |

| E         | Pad row pitch      | 1.27      | mm   |

| X1        | Pad width          | 0.60      | mm   |

| Y1        | Pad length         | 1.55      | mm   |

Note:

1. This land pattern design is based on IPC -7351

2.All feature sizes shown are at maximum material condition and a card fabrication tolerance of 0.05 mm is assumed.

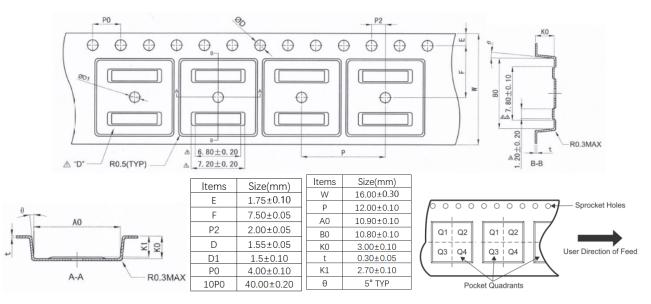

The Fig 42 illustrates the recommended land pattern details for the Pai823xB/C in a 14-pin wide body SOIC package. The table lists the values for the dimensions shown in the illustration.

#### Fig 42.14-Lead Wide Body SOIC [WB SOIC-14] Land Pattern

#### Table 19.14-Lead Wide Body SOIC [WB SOIC-14] Land Pattern Dimensions

| DIMENSION | FEATURE            | PARAMETER | UNIT |

|-----------|--------------------|-----------|------|

| C1        | Pad column spacing | 9.40      | mm   |

| E         | Pad row pitch      | 1.27      | mm   |

| X1        | Pad width          | 0.60      | mm   |

| Y1        | Pad length         | 1.90      | mm   |

Note:

1. This land pattern design is based on IPC -7351

2.All feature sizes shown are at maximum material condition and a card fabrication tolerance of 0.05 mm is assumed.

# 11. Top Marking

Fig 43.Top Marking

| Line 1 | PaiXXXXXX=Product name                    |  |  |

|--------|-------------------------------------------|--|--|

|        | YY = Work Year                            |  |  |

| Line 2 | WW = Work Week                            |  |  |

|        | ZZ=Manufacturing code from assembly house |  |  |

| Line 3 | XXXXX, no special meaning                 |  |  |

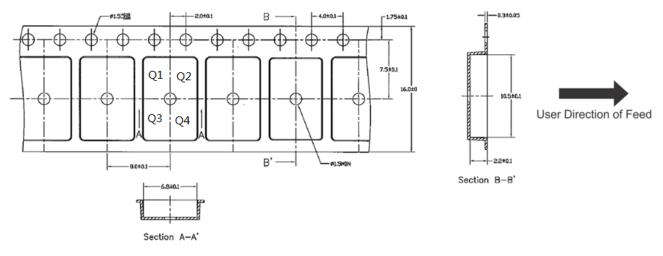

# **12.**Reel Information

Figure 44.NB SOIC-16 Reel Information-dimension unit(mm)

Note: The Pin 1 of the chip is in the quadrant Q1

Fig 45.WB SOIC-14 Reel Information-dimension unit(mm)

Note: The Pin1 of the chip is in the quadrant Q1

# 13.Ordering Guide

Table 20.Ordering Guide

| Model Name                 | Temperature<br>Range | Peak<br>Current | Rec. VDD<br>Supply Min. | Isolation<br>Rating | Package    | MSL Peak Temp <sup>1</sup> | Quantity<br>per reel |

|----------------------------|----------------------|-----------------|-------------------------|---------------------|------------|----------------------------|----------------------|

| Pai8232B-WR                | –40~125°C            | 2A/4A           | 6.5V                    | 5.0kVrms            | WB SOIC-14 | <b>Level-2-260</b> ℃       | 1500                 |

| Pai8232C-WR                | -40~125°C            | 2A/4A           | 9.2V                    | 5.0kVrms            | WB SOIC-14 | <b>Level-2-260</b> ℃       | 1500                 |

| Pai8233B-WR                | -40~125°C            | 4A/8A           | 6.5V                    | 5.0kVrms            | WB SOIC-14 | Level-2-260℃               | 1500                 |

| Pai8233C-WR                | –40~125°C            | 4A/8A           | 9.2V                    | 5.0kVrms            | WB SOIC-14 | Level-2-260℃               | 1500                 |

| Pai8233BQ-WR <sup>2</sup>  | –40~125°C            | 4A/8A           | 6.5V                    | 5.0kVrms            | WB SOIC-14 | <b>Level-2-260</b> ℃       | 1500                 |

| Pai8233CQ-WR <sup>2</sup>  | –40~125°C            | 4A/8A           | 9.2V                    | 5.0kVrms            | WB SOIC-14 | Level-2-260℃               | 1500                 |

| Pai8232B-S1R               | –40~125°C            | 2A/4A           | 6.5V                    | 3.0kVrms            | NB SOIC-16 | <b>Level-2-260</b> ℃       | 2500                 |

| Pai8232C-S1R               | –40~125°C            | 2A/4A           | 9.2V                    | 3.0kVrms            | NB SOIC-16 | Level-2-260℃               | 2500                 |

| Pai8233B-S1R               | –40~125°C            | 4A/8A           | 6.5V                    | 3.0kVrms            | NB SOIC-16 | <b>Level-2-260</b> ℃       | 2500                 |

| Pai8233C-S1R               | –40~125°C            | 4A/8A           | 9.2V                    | 3.0kVrms            | NB SOIC-16 | Level-2-260℃               | 2500                 |

| Pai8233BQ-S1R <sup>2</sup> | -40~125°C            | 4A/8A           | 6.5V                    | 3.0kVrms            | NB SOIC-16 | <b>Level-2-260</b> ℃       | 2500                 |

| Pai8233CQ-S1R <sup>2</sup> | -40~125°C            | 4A/8A           | 9.2V                    | 3.0kVrms            | NB SOIC-16 | Level-2-260℃               | 2500                 |

Note:

1. MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

2. AEC-Q100 qualified for automotive application

# **14.Important Notice and Disclaimer**

2Pai semi intends to provide customers with the latest, accurate, and in-depth documentation. However, no responsibility is assumed by 2Pai semi for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Characterization data, available modules, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only.2Pai semi reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information.2Pai semi shall have no liability for the consequences of use of the information supplied herein.

Trademarks and registered trademarks are the property of their respective owners. This document does not imply, or express copyright licenses granted hereunder to design or fabricate any integrated circuits.

Room 307-309, No.22, Boxia Road, Pudong New District, Shanghai, 201203, China 021-50850681

2Pai Semiconductor Co., Limited. All rights reserved.

http://www.rpsemi.com/

# **15. Revision History**

| Revision           | Date       | Page    | Change Record                 |

|--------------------|------------|---------|-------------------------------|

| Rev.1.0            | 2021-10-22 | All     | Initial version               |

| Rev.1.1 2022-01-13 |            | Page 7  | Update UVLO in Table 12       |

|                    | 2022-01-13 | Page10  | Update Fig 16                 |

|                    |            | Page 22 | Update Table 19               |

| Rev.1.2            | 2022-09-25 | All     | Update NB SOIC-16 information |

|                    |            | Page 24 | Update MSL3 to MSL2(Table 20) |