#### **■** General Description

AME, Inc.

The AT9173 is a voltage regulator which could convert the input voltage ranging from 1.8V to 5V to an output voltage that user settled. The regulator can provide sourcing or sinking current. The AT9173, used in conjunction with series termination resistors, provides an excellent voltage source for active termination schemes of high speed transmission lines as those seen in high speed memory buses and distributed backplane designs.

The voltage output of the regulator can be used as a termination voltage for DDR SDRAM.

Current limits in both sourcing and sinking mode, plus on-chip thermal shutdown make the circuit tolerant of the output fault conditions.

# ■ Applications

DDRI/DDRII Memory Termination Supply

Active Termination Buses

Desktop PC,NoTebook,Server and workstation

Graphic Card

Set Top Box

Embedded System

#### **■** Features

Support Both DDR I (1.25VTT) and DDR II (0.9VTT) Requirements

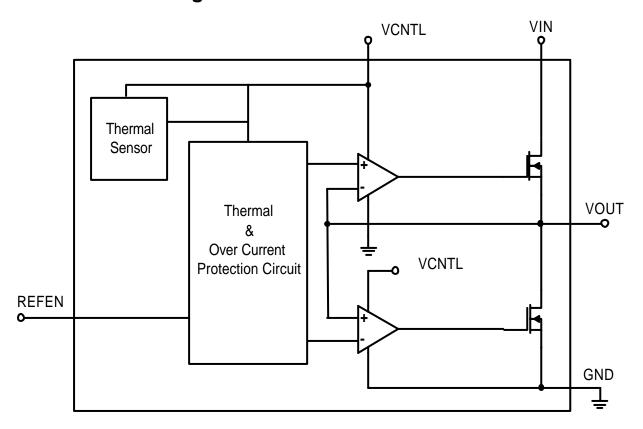

Capable of Sourcing and Sinking Current

Current-limiting Protection

Thermal Protection

Integrated Power MOSFETs

Generates Termination Voltages for SSTL-2

High Accuracy Output Voltage at Full-Load

Adjustable V<sub>OUT</sub> by External Resistors

Minimum External Components

Shutdown for Standby or Suspend Mode

Operation with High-impedance Output

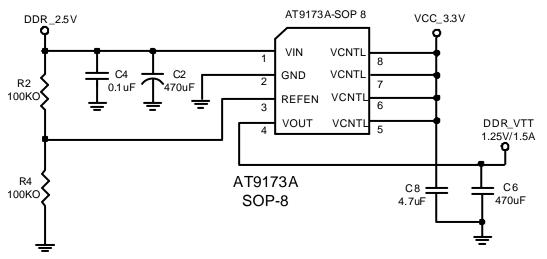

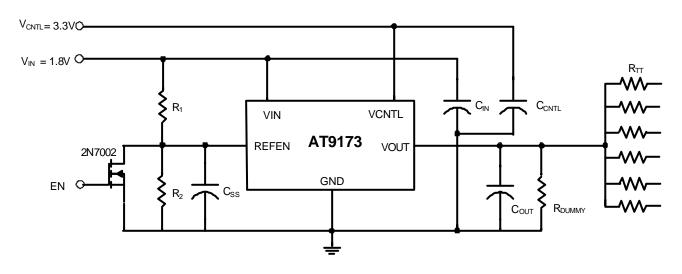

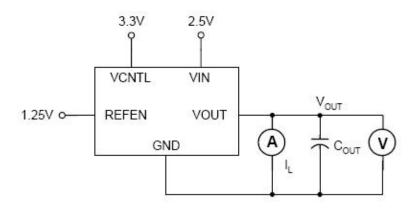

## ■ Typical Application

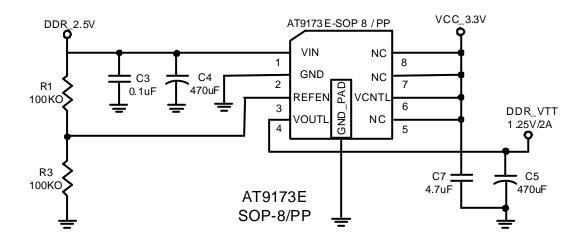

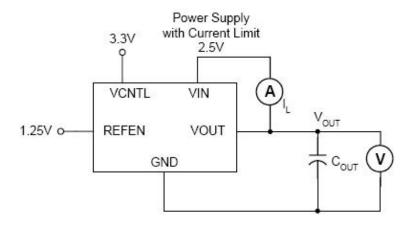

# ■ Typical Application(Contd.)

# **■** Function Block Diagram

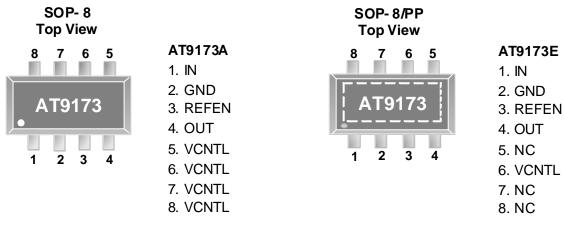

# **■** Pin Configuration

# **■** Pin Description

| Pin name | Pin Description                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN       | Input voltage pin which supplies current to the $V_{\text{OUT}}$ pin. Connect this pin to a well-decoupled voltage to prevent the input rail from dropping during large load transient. A large and low ESR capacitor is recommended to use that should be placed as close as possible to the $V_{\text{IN}}$ pin.                                                                                    |

| GND      | Ground pin. Tie directly to ground plance.                                                                                                                                                                                                                                                                                                                                                            |

| VCNTL    | Voltage control pin which supplies the internal control circuitry and provides the drive voltage. The driving capability of output current is proportioned to the VCNTL. Connect this pin to 5V bias supply to handle large output current with at least 1uF capacitor from this pin to GND. An important note is that $V_{\text{IN}}$ should be kept lower or equal to VCNTL.                        |

| REFEN    | Reference voltage input and active low shutdown control pin. Two resistors dividing down the V <sub>IN</sub> voltage on this pin to create the regulatedoutput voltage. Pulling this pin to GND to turn off the device by an open-drain, such as 2N7002 N-Channel MOSFET.                                                                                                                             |

| OUT      | Regulator output. $V_{OUT}$ is regulated from REFEN voltage that is used to terminate the bus resistors. It is capable of sinking and sourcing current while regulating the output rail. To maintain adequate large signal transient response, typical value of 1000uF electrolytic capacitor with 10uF ceramic capacitors are recommended to reduce the effects of current transients on $V_{OUT}$ . |

| NC*      | No Connection. Not internal connected.                                                                                                                                                                                                                                                                                                                                                                |

| GND Pad* | Connected to GND plance for better heat dissipation.                                                                                                                                                                                                                                                                                                                                                  |

<sup>\*</sup> By SOP-8/PP only

# ■ Ordering Information

| Part Number | Marking                             | Output Voltage | Package  | Operating Temp. Range |

|-------------|-------------------------------------|----------------|----------|-----------------------|

| AT9173AG    | AT9173AG<br>yyww* AB<br>xxxxxxx##** | ADJ            | SOP-8    | -25°C to +85°C        |

| AT9173EG    | AT9173EG<br>yyww* AC<br>xxxxxxx##** | ADJ            | SOP-8/PP | -25 C to +65 C        |

#### Note:

<sup>\*</sup> yy and ww represents the data code.

<sup>\*\*</sup> XXXXXXX represents the wafer lot number, ## represents the wafer number

# ■ Absolute Maximum Ratings

| Parameter                             | Symbol            | Maximum | Unit |

|---------------------------------------|-------------------|---------|------|

| Input Voltage. V <sub>IN</sub> to GND | V <sub>IN</sub>   | 6       | V    |

| VCNTL to GND                          | V <sub>CNTL</sub> | 6       | V    |

| ESD Rating (Human Body Mode)          | V <sub>ESD</sub>  | 2       | KV   |

| Storage Temperature                   | T <sub>STG</sub>  | 150     | °С   |

| Lead Temperature (Soldering. 5sec)    | TL                | 245     | °c   |

# **■** Recommended Operating Conditions

| Parameter                                | Symbol            | Rating     | Unit |

|------------------------------------------|-------------------|------------|------|

| Supply Voltage 1                         | $V_{IN}$          | 1.8 or 2.5 | V    |

| Supply Voltage 2                         | $V_{CNTL}$        | 3.3        | V    |

| Output Current of V <sub>OUT</sub> Pin * | *I <sub>OUT</sub> | -2 to 2    | Α    |

| Junction Temperature                     | $T_J$             | -25 to 125 | °С   |

<sup>\*</sup>The symbol "+" means the VOUT sources current to load; the symbol "-" means the VOUT sinks current to GND

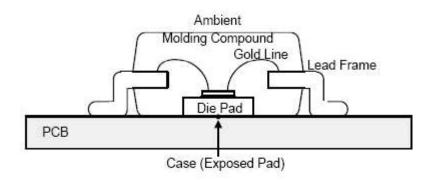

#### **■** Thermal Characteristics

| Parameter                  | Package  | Die Attch               | Symbol              | Maximum | Unit |

|----------------------------|----------|-------------------------|---------------------|---------|------|

| Thermal Resistance*        | SOP-8    | Non-Conductive<br>Epoxy | 0                   | 55      |      |

| (Junction to Case)         | SOP-8/PP | Conductive<br>Epoxy     | θ <sub>JC</sub>     | 19      | °C/W |

| Thermal Resistance         | SOP-8    | Non-Conductive<br>Epoxy |                     | 120     | C/VV |

| (Junction to Ambient)      | SOP-8/PP | Conductive<br>Epoxy     | $\theta_{JA}$       | 84      |      |

| Internal Power Dissipation | SOP-8    | Non-Conductive<br>Epoxy | D.                  | 1300    | mW   |

| Internal Power Dissipation | SOP-8/PP | Conductive<br>Epoxy     | P <sub>D</sub> 1450 | IIIVV   |      |

# **■** Electrical Specifications

Limits in standard typeface are for  $\rm T_A=25~$  , unless otherwise specified:  $\rm V_{IN}=2.5V,~V_{CNTL}=3.3V,~V_{REFEN}=0.5V_{IN}.$

| Parameter                              | Symbol             | Test Condition                                        |     | Тур     | Max | Units |

|----------------------------------------|--------------------|-------------------------------------------------------|-----|---------|-----|-------|

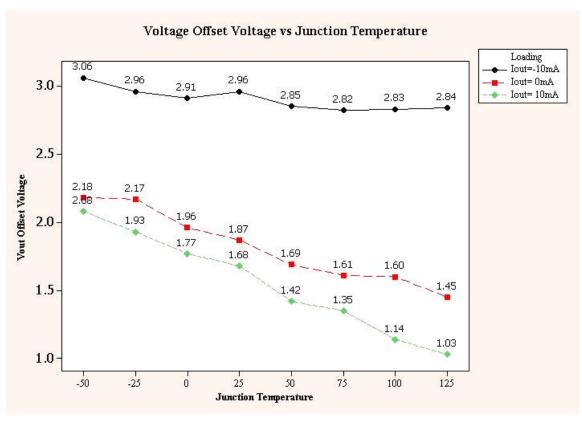

| Output Offset Voltage                  | Vos                | I <sub>OUT</sub> =0A (Note 1)                         | -20 | 0       | 20  | mV    |

| Load Regulation                        | M                  | I <sub>L</sub> =0~1.5A (Fig 4)                        | -20 | 0       | 20  |       |

| (DDR 1/2)                              | $V_{LOAD}$         | I <sub>L</sub> =0~-1.5A                               | -20 | 0       | 20  | mV    |

| Input Voltage Range (DDR               | $V_{IN}$           | KEEP V <sub>CNTL</sub> ≥ V <sub>IN</sub> on operation | 1.6 | 2.5/1.8 | 4   | W     |

| 1/2)                                   | $V_{CNTL}$         | power on and power off                                | 2.5 | 3.3     | 6   | V     |

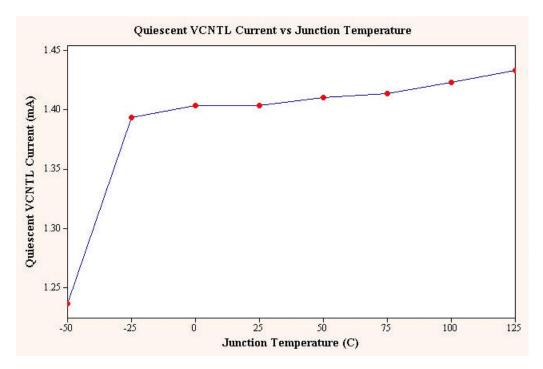

| Operating Current of V <sub>CNTL</sub> | I <sub>CNTL</sub>  | No Load                                               |     | 1.4     |     | mA    |

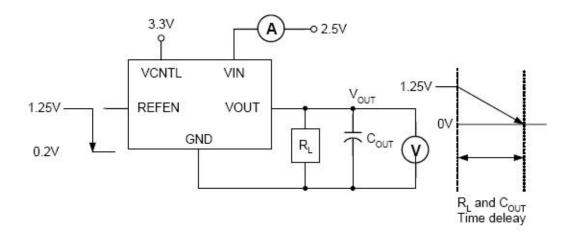

| Current In Shutdown Mode               | I <sub>SHDN</sub>  | $V_{REFEN}$ < 0.2V, $R_L$ =180 $\Omega$ (Fig 5)       |     | 25.6    |     | μд    |

| Short Circuit Protection               |                    |                                                       |     |         |     |       |

| SOP-8 Current Limit                    | I <sub>LIMIT</sub> | Fig 6,7                                               | 2.1 |         |     | Α     |

| PSOP-8 Current Limit                   | I <sub>LIMIT</sub> | Fig 6,7                                               | 2.4 |         |     | Α     |

| Over Temperature Protection            |                    |                                                       |     | ,       |     |       |

| Thermal Shutdown<br>Temperature        | T <sub>SD</sub>    | $3.3V \le V_{CNTL} \le 5V$                            | 125 |         |     | °C    |

| Thermal Shutdown<br>Hysteresis         |                    | Guaranteed by design                                  |     | 30      |     |       |

Note1:  $V_{OS}$  offset is the voltage measurement defined as  $V_{OUT}$  subtracted from  $V_{REFEN}$ .

### ■ Application Information

AME, Inc.

$R_1 = R_2 = 100KO, R_{TT} = 50O / 33O / 25O$

$C_{OUT(MIN)} = 10$ uF (Ceramic) + 1000uF under the worst case testing condition

$R_{DUMMY} = 1$ KO as for  $V_{OUT}$  discharge when  $V_{IN}$  is not presented but  $V_{CNTL}$  is presented

$C_{SS} = 1uF$ ,  $C_{IN} = 470uF$  (Low ESR),  $C_{CNTL} = 47uF$

# **■** Application Circuit

Typical application circuit is used as a regulator to provide termination voltage in double data rate (DDR) memory system. The regulator could source and sink up to 2A peak current. The output voltage will follow REFEN which generated by two external dividing resistors down from  $V_{\rm IN}$  or to the desired output voltage set externally by forcing a voltage level to REFEN pin. To add a shutdown function , connect a small transistor to REFEN pin. To perform shutdown function , put a logic high 5V signal to EN yield a low (0V) to REFEN pin thus force output voltage to zero voltage. The capacitor Css is used to softstart the output voltage since  $V_{\rm OUT}$  will follow REFEN.

Time constant for this circuit is Css\*(R1//R2). The Css could also used as the bypass capacitor to filter out noise in REFEN pin. So carefully layout should put Css close to REFEN pin to maintain noise immunity. The  $C_{\text{IN}}$  an  $C_{\text{CNTL}}$  is used as power decoupling capacitor.  $C_{\text{OUT}}$  is composed of 10uF ceramic plus 1000uF electrolyte capacitors. The first one is to used as high frequency filter and the second one is used to reduce voltage drop during load regulating.

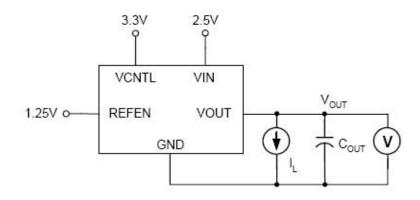

### ■ General Regulator

The AT9173 can be used as a general regulator. To get a desired output voltage, put a reference voltage to REFEN pin or dividing resistors down a input voltage source. To drive inside N-Channel MOSFET the  $V_{\text{CNTL}}$  should be larger than  $V_{\text{IN}}$  to get enough driving voltage. The minimum dropout voltage could be  $I_{\text{OUT}}^*$ 0.1, where  $I_{\text{OUT}}$  is the output current.

### ■ Layout issue

Place a bypass capacitor as close as possible to  $V_{\text{IN}}$  and  $V_{\text{CNTL}}$  pin is necessary. A low ESR capacitor is recommended for this bypass capacitor. Use wide and short PCB traces to connect in between  $V_{\text{IN}}$  power source  $V_{\text{OUT}}$  to reduce PCB resistance thus to reduce undesired power dissipation.

#### **■** Thermal issue

AT9173 has a internal thermal protection to protect the device at any overload conditions. For safety reason the operation junction temperature should not exceed 125 . The dissipation of the device is

$$P_D = (V_{IN} - V_{OUT}) x I_{OUT}$$

And also the maximum power dissipation is

$$P_{D,MAX} = (T_{J,MAX} - T_A)/\boldsymbol{q}_{JA}$$

Where Tj,max is the maximum operation junction 125 degree C, Ta is the ambient temperature and the is  $q_{\rm JA}$  the junction to ambient thermal resistance. The junction to ambient thermal resistance is 70  $\,$  /W for exposed pad SOP-8 package. It can be dramatically reduced by placing a large area PCB trace under exposed pad to emit heat generated by the die attached to the exposed pad.

#### **■ Test Circuit**

AME, Inc.

Fig 4: Output Voltage Tolerance,  $V_{OUT}$

Fig 5: Current in Shutdown Mode,  $I_{\rm SHDN}$

Figure 6: Current Limit for High Side,  $\mathbf{I}_{\text{CLHIGH}}$

Figure 7: Current Limit for Low Side,  $I_{\rm CLLOW}$

# **■** Typical Characteristics

AME, Inc.

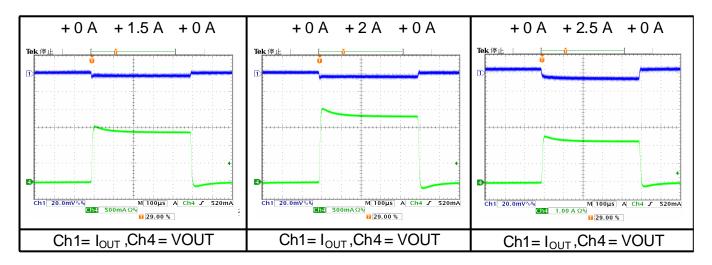

#### **■** Operation Waveforms DDR1

#### **Load Transient Response**

$\begin{aligned} & \mathsf{V_{IN}} \text{=} 2.5 \mathsf{V}, \ \mathsf{V_{CNTL}} \text{=} 3.3 \mathsf{V} \\ & \mathsf{V_{REF}} \text{ is } 1.25 \mathsf{V} \text{ supplied by a regulator } \\ & \mathsf{C_{OUT}} \text{=} 1000 \text{uF} / 35 \mathsf{V} \\ & \mathsf{I_{OUT}} \text{ slew rate } = \text{+-}0.25 \text{A/mS} \end{aligned}$

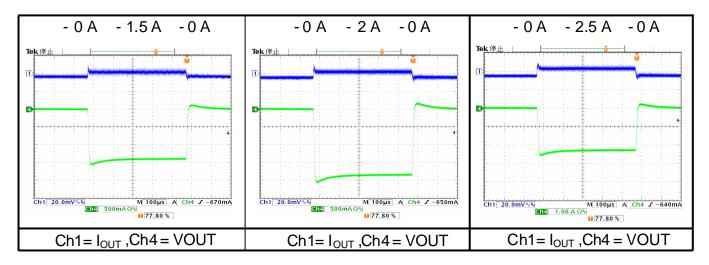

# **Load Transient Response**

$$\begin{split} & \text{V}_{\text{IN}}\text{=}2.5\text{V}, \text{ V}_{\text{CNTL}}\text{=}3.3\text{V} \\ & \text{V}_{\text{REF}} \text{ is } 1.25\text{V} \text{ supplied by a regulator } \\ & \text{C}_{\text{OUT}}\text{=}1000\text{uF}/35\text{V} \\ & \text{I}_{\text{OUT}} \text{ slew rate = +-0.25A/mS} \end{split}$$

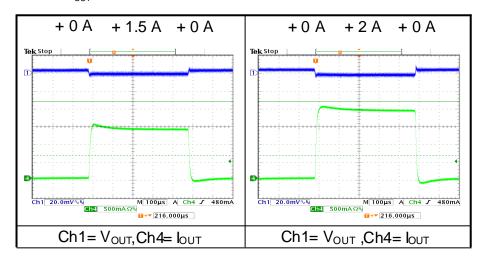

#### **■** Operation Waveforms DDR2

AME, Inc.

# **Load Transient Response**

$$\begin{split} & \text{V}_{\text{IN}}\text{=}1.8\text{V}, \text{ V}_{\text{CNTL}}\text{=}3.3\text{V} \\ & \text{V}_{\text{REF}} \text{ is } 0.9\text{V} \text{ supplied by a regulator } \\ & \text{C}_{\text{OUT}}\text{=}1000\text{uF}/35\text{V} \\ & \text{I}_{\text{OUT}} \text{ slew rate = +-0.25A/mS} \end{split}$$

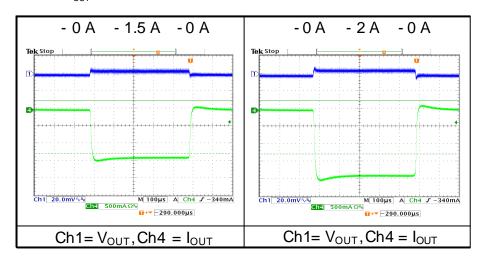

# **Load Transient Response**

$m V_{IN}$ =1.8V,  $m V_{CNTL}$ =3.3V  $m V_{REF}$  is 0.9V supplied by a regulator  $m C_{OUT}$ =1000uF/35V  $m I_{OUT}$  slew rate = +-0.25A/mS

#### ■ Date Code Rule

| Marking |          |          | Date     | Code     | Year |

|---------|----------|----------|----------|----------|------|

| Α       | Α        | Α        | W        | W        | xxx0 |

| Α       | Α        | Α        | W        | W        | xxx1 |

| Α       | Α        | Α        | <u>W</u> | W        | xxx2 |

| Α       | Α        | Α        | <u>W</u> | W        | xxx3 |

| Α       | Α        | <u>A</u> | W        | W        | xxx4 |

| Α       | Α        | <u>A</u> | W        | W        | xxx5 |

| Α       | Α        | <u>A</u> | <u>W</u> | W        | xxx6 |

| Α       | Α        | <u>A</u> | <u>W</u> | W        | xxx7 |

| Α       | <u>A</u> | Α        | W        | W        | 8xxx |

| Α       | <u>A</u> | Α        | W        | <u>W</u> | xxx9 |

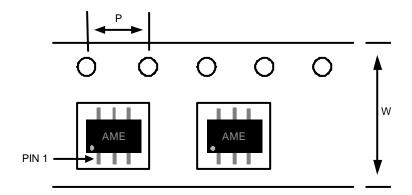

# ■ Tape and Reel Dimension

#### **SOP-8**

#### Carrier Tape, Number of Components Per Reel and Reel Size

| Package | Carrier Width (W) | Pitch (P)  | Part Per Full Reel | Reel Size |

|---------|-------------------|------------|--------------------|-----------|

| SOP-8   | 12.0±0.1 mm       | 4.0±0.1 mm | 2500pcs            | 330±1 mm  |

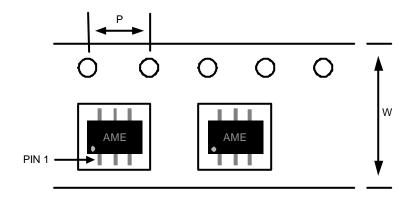

# ■ Tape and Reel Dimension

#### SOP-8/PP

Carrier Tape, Number of Components Per Reel and Reel Size

| Package  | Carrier Width (W) | Pitch (P)  | Part Per Full Reel | Reel Size |

|----------|-------------------|------------|--------------------|-----------|

| SOP-8/PP | 12.0±0.1 mm       | 4.0±0.1 mm | 2500pcs            | 330±1 mm  |

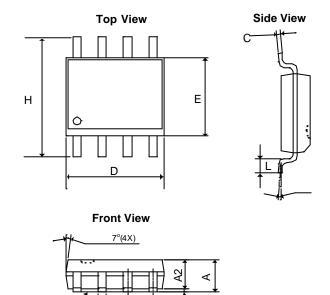

# **■ Package Dimension**

SOP-8

| SYMBOLS          | MILLIM | ETERS | INCHES  |         |  |

|------------------|--------|-------|---------|---------|--|

| STIVIBULS        | MIN    | MAX   | MIN     | MAX     |  |

| Α                | 1.35   | 1.75  | 0.05315 | 0.0689  |  |

| $\mathbf{A}_{1}$ | 0.10   | 0.30  | 0.00394 | 0.01181 |  |

| A2               | 1.473  | REF   | 0.0579  | 99 REF  |  |

| В                | 0.33   | 0.51  | 0.01299 | 0.02008 |  |

| С                | 0.19   | 0.25  | 0.00748 | 0.00984 |  |

| D                | 4.80   | 5.33  | 0.18898 | 0.20984 |  |

| E                | 3.80   | 4.00  | 0.14961 | 0.15748 |  |

| е                | 1.27   | BSC   | 0.0500  | 00 BSC  |  |

| L                | 0.40   | 1.27  | 0.01575 | 0.05000 |  |

| Н                | 5.80   | 6.30  | 0.22835 | 0.24803 |  |

| у                | -      | 0.10  | -       | 0.00394 |  |

| q                | 0°     | 8°    | 0°      | 8°      |  |

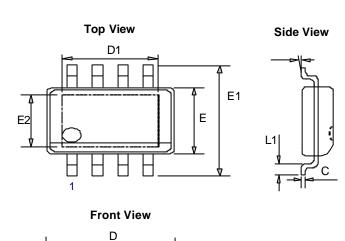

SOP-8/PP

| SYMBOLS    | MILLIM | IETERS | INCHES   |       |  |

|------------|--------|--------|----------|-------|--|

| STWIBULS   | MIN    | MAX    | MIN      | MAX   |  |

| Α          | -      | 1.750  | -        | 0.069 |  |

| <b>A</b> 1 | 0      | 0.150  | 0        | 0.006 |  |

| A2         | 1.350  | 1.600  | 0.053    | 0.063 |  |

| С          | 0.100  | 0.250  | 0.004    | 0.010 |  |

| E          | 3.750  | 4.150  | 0.148    | 0.163 |  |

| E1         | 5.700  | 6.300  | 0.224    | 0.248 |  |

| L          | 0.300  | 0.900  | 0.012    | 0.035 |  |

| b          | 0.310  | 0.510  | 0.012    | 0.020 |  |

| D          | 4.720  | 5.120  | 0.186    | 0.202 |  |

| е          | 1.270  | BSC    | 0.05 BSC |       |  |

| q          | 0°     | 8°     | 0°       | 8°    |  |

| E2         | 2.150  | 2.500  | 0.085    | 0.098 |  |

| D1         | 2.150  | 3.400  | 0.085    | 0.134 |  |

E-Mail: sales@ame.com.tw

#### Life Support Policy:

These products of AME, Inc. are not authorized for use as critical components in life-support devices or systems, without the express written approval of the president of AME, Inc.

AME, Inc. reserves the right to make changes in the circuitry and specifications of its devices and advises its customers to obtain the latest version of relevant information.

© AME, Inc., December 2007 Document: ATT-DS9173-C.04

# **Corporate Headquarter AME, Inc.**

2F, 302 Rui-Guang Road, Nei-Hu District Taipei 114, Taiwan.

Tel: 886 2 2627-8687 Fax: 886 2 2659-2989

# U.S.A (Subsidiary) Analog Microelectronics, Inc.

3100 De La Cruz Blvd., Suite 201 Santa Clara, CA. 95054-2046

Tel: (408) 988-2388 Fax: (408) 988-2489