### 2.5A SWITCH STEP DOWN SWITCHING REGULATOR

### Features

- 2.5A Internal Switch

- Operating Input Voltage from 4.8V to 22V

- 3.3V ±2% Reference Voltage

- Output Voltage : APW1172 - adjustable from 1.235V to 20V

- Low Dropout Operation: 100% Duty Cycle

- 250KHz Internally Fixed Frequency

- Voltage Feed-Forward

- Zero Load Current Operation

- Internal Current Limit

- Inhibit for Zero Current Consumption

- Synchronization

- Protection Against Feedback Disconnection

- Thermal Protection

- External Soft-Start

- Over-Voltage Protection

- Lead Free Available (RoHS Compliant)

# **Applications**

- Consumer: STB, DVD, TV, VCR, Car Radio, LCD monitors

- Networking: XDSL, Modems, DC-DC Modules

- Computer: Printers, Audio/Graphic Cards, Optical Storage, Hard Disk Drive

- Industrial: Chargers, Car Battery DC-DC

Converters

### **General Description**

The APW1172 is a step down monolithic power switching regulator with a switching current limit of 3.8A so it is able to deliver more than 2.5ADC current to the load depending on the application conditions.

The output voltage can be set from 1.235V to 22V.The high current level is also achieved utilize an SO8 package with exposed pad frame. The type of package allows to re-duce the Rth (j-amb) down to approximately 45°C/W.

An internal oscillator fixes the switching frequency at 250KHz.

Having a minimum input voltage of 4.8V only, it is particularly suitable for 5V bus, available in all computer related applications.

Pulse by pulse current limit with the internal frequency modulation offers an effective constant current short circuit protection.

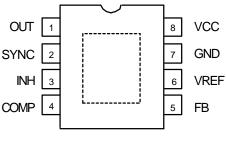

# **Pin Description**

SOP-8-P (Top View)

= Thermal Pad (connected to GND plane for better heat dissipation)

ANPEC reserves the right to make changes to improve reliability or manufacturability without notice, and advise customers to obtain the latest version of relevant information to verify before placing orders.

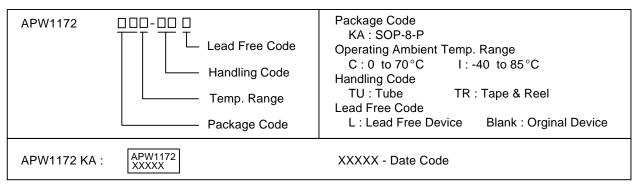

### **Ordering and Marking Information**

Note: ANPEC lead-free products contain molding compounds/die attach materials and 100% matte tin plate termination finish; which are fully compliant with RoHS and compatible with both SnPb and lead-free soldiering operations. ANPEC lead-free products meet or exceed the lead-free requirements of IPC/JEDEC J STD-020C for MSL classification at lead-free peak reflow temperature.

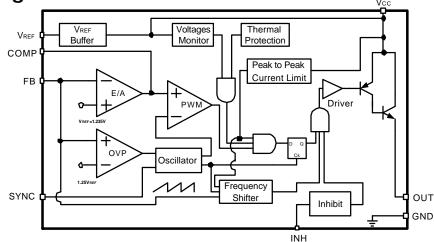

### **Block Diagram**

### **Absolute Maximum Ratings**

| Symbol | Parameter                                       | Value              | Unit |

|--------|-------------------------------------------------|--------------------|------|

| Vcc    | Input voltage (VCC to GND)                      | 25                 | V    |

| Vout   | Output DC voltage                               | -1 to 25           | V    |

| Vio    | COMP and FB to GND                              | -0.7 ~ Vcc         | V    |

| Іоит   | Output current                                  | 0 to current limit | А    |

| Vref   | VREF to GND                                     | 3.3                | V    |

| PD     | Average Power Dissipation, T <sub>A</sub> < 50° | 2.2                | W    |

| ТJ     | Junction Temperature                            | 150                | °C   |

| Tstg   | Storage Temperature                             | -65 ~ 150          | °C   |

| Tsdr   | Soldering Temperature, 10 seconds               | 300                | °C   |

| Vesd   | Minimum ESD rating (Human body mode)            | ±3                 | KV   |

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

### **Pin Function Description**

| No. | PIN  | Description                                                                                                                                                            |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | OUT  | Regulator Output.                                                                                                                                                      |

| 2   | SYNC | Master/Slave synchonization.                                                                                                                                           |

| 3   | INH  | A logical signal (active high) disables the device. If INH not used the pin must be connected to GND. When it is open an internal pull-up disable the device.          |

| 4   | СОМР | E/A output for frequency compensation.                                                                                                                                 |

| 5   | FB   | Feedback input. Connecting directly to this pin results in an output voltage of 1.235V(APW1172). An external resistive divider is required for higher output voltages. |

| 6   | VREF | 3.3V reference voltage output, no Capacitor Is requested for stability.                                                                                                |

| 7   | GND  | Ground.                                                                                                                                                                |

| 8   | VCC  | Unregulated DC input voltage.                                                                                                                                          |

### **Thermal Characteristics**

| Symbol | Parameter                                          | Value | Unit |

|--------|----------------------------------------------------|-------|------|

| θја    | Junction to ambient thermal resistance in free air |       | °C/W |

\* The area of the thermal pad is 4.5mm X 2mm and the GND plane is 60mm X 60mm. Connect the thermal pad and the GND plane by 8 vias.  $T_A=25^{\circ}C$ .

### **Electrical Characteristics**

The \* denotes the specifications that apply over  $T_A = -40 \sim 85^{\circ}$ C. Typical values are at  $T_A = 25^{\circ}$ C. V<sub>CC</sub> = 12V unless otherwise specified.

| Symbol                | Parameter                     | Test condition      |     | A   | Unit |      |      |

|-----------------------|-------------------------------|---------------------|-----|-----|------|------|------|

| Symbol                | Falameter                     | rest condition      |     |     | Тур  | Мах  | Onit |

| Vcc                   | Operating input voltage range | Vo= 1.235V; lo= 2A  | *   | 4.7 |      | 22   | V    |

| Vuvlo                 | UVLO threshold voltage        | Vcc rising          | *   | 3.8 | 4.2  | 4.6  | V    |

|                       | Hysteresis                    |                     |     |     | 0.3  |      | V    |

| Vd                    | Dropout voltage               | Vcc = 4.8V; Io = 2A | *   |     | 1.0  | 1.2  | V    |

| Іім                   | Maximum limiting current      | Vcc = 4.8V to 22V   | *   | 3.3 | 3.8  | 4.3  | А    |

| fs                    | Switching frequency           | Main design         | *   | 200 | 250  | 300  | KHz  |

| is Switching nequency | Main design                   |                     | 205 | 250 | 295  | NI1Z |      |

|                       | Duty cycle                    |                     |     | 0   |      | 100  | %    |

# **Electrical Characteristics (Cont.)**

The \* denotes the specifications that apply over  $T_A = -40 \sim 85^{\circ}C$ . Typical values are at  $T_A = 25^{\circ}C$ . Vcc = 12V unless otherwise specified.

| Symbol    | Parameter                         | Test condition                                                  |   | APW1172 |       |       | Unit |

|-----------|-----------------------------------|-----------------------------------------------------------------|---|---------|-------|-------|------|

| Symbol    | Parameter                         | Test condition                                                  |   | Min     | Тур   | Max   | Unit |

| Dynamie   | c Characteristics                 |                                                                 |   |         |       |       |      |

| Vfb       | Voltage feedback                  | 4.8V < Vcc < 22V, 20Ma < lo < 2A                                |   | 1.22    | 1.235 | 1.25  | V    |

| VFB       | APW1172                           | 4.00 < 0.00 < 220, 2000 < 10 < 2A                               | * | 1.198   | 1.235 | 1.272 | v    |

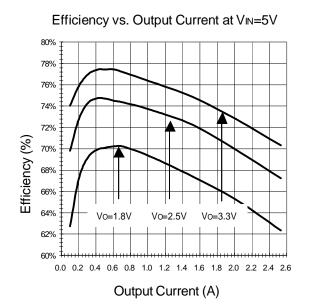

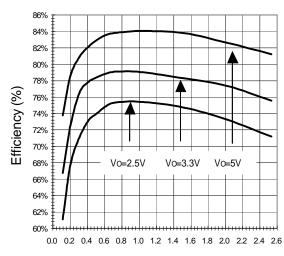

| η         | Efficiency                        | Vo = 5V, Vcc = 12V, Iout = 1A                                   |   |         | 84    |       | %    |

| DC Chai   | racteristics                      |                                                                 |   |         |       |       |      |

| Iqop      | Total Operating Quiescent Current |                                                                 | * |         |       | 12    | mA   |

| lq        | Quiescent Current                 | Duty Cycle = 0; VFB = 1.5V                                      |   |         |       | 10    | mA   |

| 1.0       | Total Stand by Quiacoant Qurrent  | Vinh > 2.2V                                                     | * |         | 50    | 100   | μΑ   |

| lqst-by   | Total Stand-by Quiescent Current  | Vcc = 22V; VINH > 2.2V                                          | * |         | 80    | 150   | μA   |

| Inhibit   |                                   |                                                                 |   |         |       |       |      |

| Vinh      | INH Threshold Voltage             | Device ON                                                       |   | 1.1     | 1.3   | 1.5   | V    |

| VINIT     | intesticia voltage                | Device OFF                                                      |   | 1.2     | 1.4   | 1.6   | V    |

|           | INH Pull-Up Current               | Vinh < 3V                                                       |   |         | 1     |       | μA   |

|           | Maximum INH Voltage               | INH = 0A                                                        |   |         | 4.3   |       | V    |

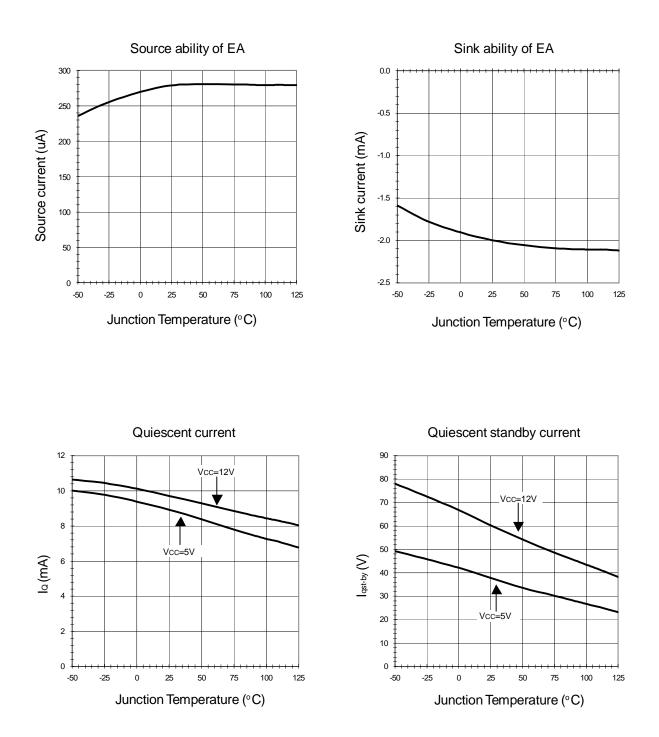

| Error An  | nplifier                          |                                                                 |   |         | •     |       |      |

| Vон       | High Level Output Voltage         | Vfb = 1V                                                        |   | 3.5     | 3.8   |       | V    |

| Vol       | Low Level Output Voltage          | Vfb = 1.5V                                                      |   |         |       | 0.4   | V    |

| IO source | Source Output Current             | Vсомр = 1.9V; Vfb = 1V                                          |   | 200     | 300   |       | μA   |

| O sink    | Sink Output Current               | Vсомр = 1.9V; Vfb = 1.5V                                        |   | 1       | 1.5   |       | mA   |

| Ifb       | Source Bias Current               | Vfb = 1.5V                                                      |   |         | 2.5   | 4     | μΑ   |

|           | Maximum FB Voltage                | Іғв = 0µА                                                       |   |         | 2.1   |       | V    |

| gm        | Trans-conductance                 | VFB = 1.255V to 1.215V, ICOMP =<br>-0.1mA to 0.1mA VCOMP = 1.9V |   |         | 2.3   |       | mA/V |

|           | unction                           |                                                                 |   |         |       |       |      |

|           | High Input Voltage                | Vcc = 4.8 to 22V                                                |   | 2.5     |       | Vref  | V    |

|           | Low Input Voltage                 | VCC = 4.8V to 22V                                               |   |         |       | 0.74  | V    |

|           | Slave Sink Current                | VSYNC = 0.74V                                                   |   | 0.11    |       | 0.25  | m^   |

|           | Slave Slink Curtefil              | VSYNC = 2.33V                                                   |   | 0.21    |       | 0.45  | mA   |

|           | Master Output Amplitude           | ISOURCE = 3mA                                                   |   | 2.75    | 3     |       | V    |

|           | Output Pulse Width                | No load, Vsync = 1.65V                                          |   | 0.2     | 0.35  |       | μs   |

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005 www.anpec.com.tw

# **Electrical Characteristics (Cont.)**

The \* denotes the specifications that apply over  $T_A = -40 \sim 85^{\circ}C$ . Typical values are at  $T_A = 25^{\circ}C$ . Vcc = 12V unless otherwise specified.

| Symbol  | Parameter                                    | Test condition                         |   | APW1172 |     |       | 11   |  |

|---------|----------------------------------------------|----------------------------------------|---|---------|-----|-------|------|--|

| Symbol  | Parameter                                    | Test condition                         |   | Min     | Тур | Max   | Unit |  |

| Referen | ce Section                                   |                                        |   |         |     |       |      |  |

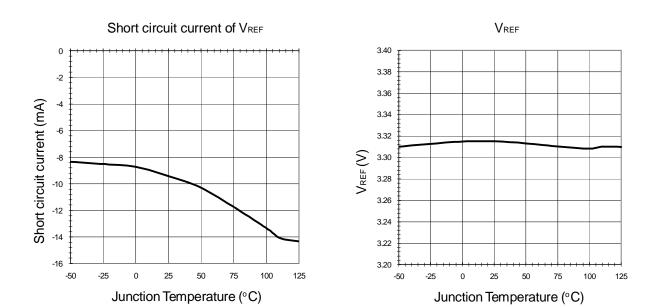

|         |                                              | Iref = 0mA                             |   | 3.234   | 3.3 | 3.366 | V    |  |

| Vref    | VREF Output Voltage                          | IREF = 0mA to 5mA, $Vcc = 4.4A$ to 22V | * | 3.2     | 3.3 | 3.399 | V    |  |

|         | Line Regulation                              | IREF = $0mA$ , Vcc = $4.4A$ to $22V$   |   |         | 5   | 10    | mV   |  |

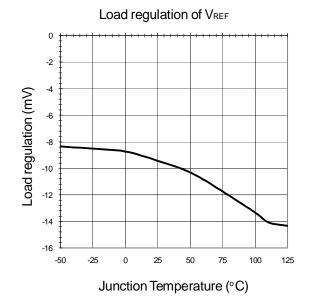

|         | Load Regulation                              | IREF = 0mA to 5mA                      |   |         | 8   | 15    | mV   |  |

|         | Short Circuit Current                        |                                        |   | 10      | 18  | 30    | mA   |  |

| Other   |                                              |                                        |   |         |     |       |      |  |

|         | Thermal Limiting Protection                  |                                        |   |         | 160 |       | °C   |  |

|         | Hysteresis                                   |                                        |   |         | 30  |       | °C   |  |

|         | Over-Voltage Protection<br>Threshold Voltage | VCOMP = 0.8V                           | * | 120     | 125 | 130   | %    |  |

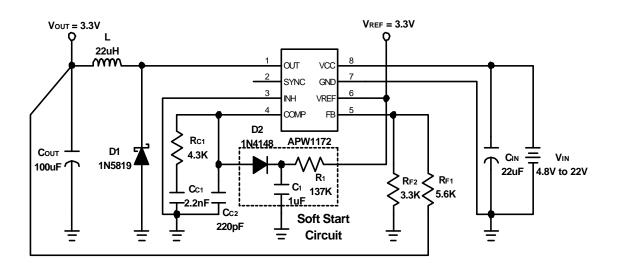

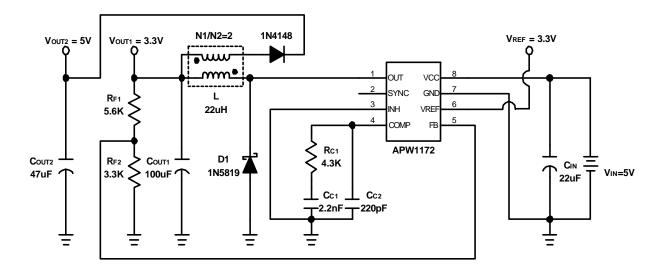

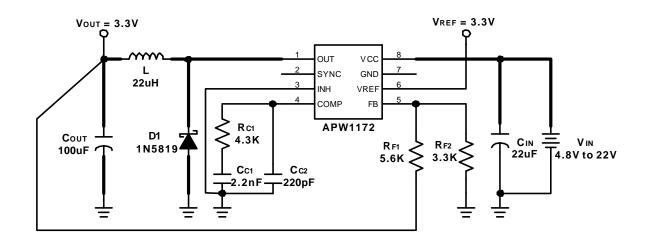

# **Typical Application Circuit**

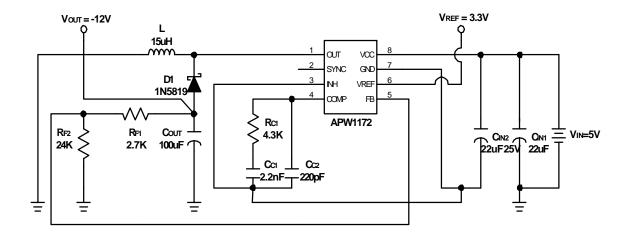

## **Other Application Circuits**

Dual output voltage application

BuckBoost regulator

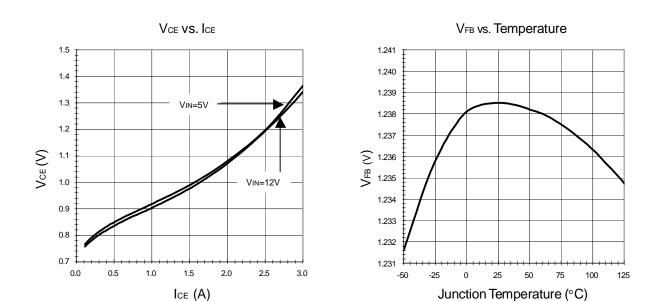

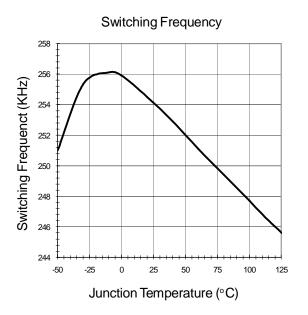

# **Typical Operating Characteristics**

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

# Typical Operating Characteristics (Cont.)

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

# Typical Operating Characteristics (Cont.)

Efficiency vs. Output Current at VIN=12V

Output Current (A)

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

## Typical Operating Characteristics (Cont.)

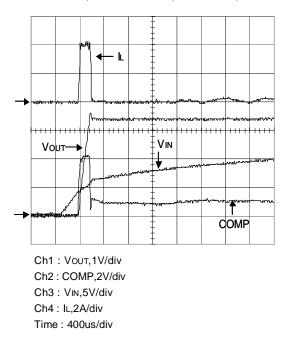

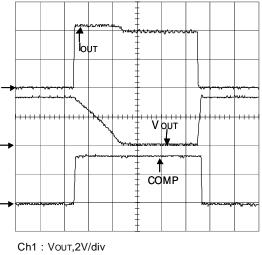

### **Operating waveforms**

### 1. Power ON (no SS) :

- VIN = 12V, VOUT = 3.3V

- $C_{IN} = 22\mu F$ ,  $C_{OUT} = 220\mu F$ ,  $L = 15 \mu H$

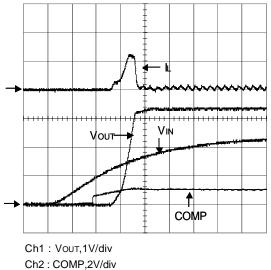

#### 2. Power ON (external SS) :

- VIN = 12V, VOUT = 3.3V

- $C_{\text{IN}}=22\mu F,\,C_{\text{OUT}}=220\mu F,\,L=15\;\mu H$

Ch2 : COMP,2V/d Ch3 : VIN,5V/div Ch4 : I∟,2A/div Time : 1ms/div

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

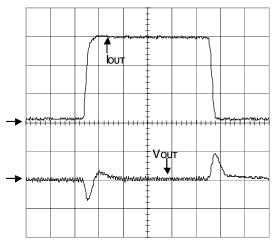

### **Operating waveforms (Cont.)**

### 3. Current Limit :

-  $C_{IN} = 22\mu F$ ,  $C_{OUT} = 220\mu F$ ,  $L = 15 \mu H$

Ch1 : VOUT,2V/div Ch2 : COMP,2V/div Ch3 : IOUT,2A/div Time : 2ms/div

# **Functional Description**

### Power-On-Reset

A Power-On-Reset circuit monitors input voltages at VCC pin to prevent wrong logic controls. The POR function initiates immediately by the inductor current with it's limit after the supply voltage exceed firstly it's threshold voltage after powering on.

### **Output Voltage Regulation**

An error amplifier working with a temperature-compensated 1.235V reference. The error amplifier designed with high bandwidth and DC gain provides very fast transient response and less load regulation. It compares the reference with the feedback voltage and amplifies the difference in it's output called error signal. The error signal feeds into the input terminal of PWM

### 4. Load Transient :

- V<sub>IN</sub> = 12V,V<sub>OUT</sub> = 3.3V

- C<sub>IN</sub> = 22μF, C<sub>OUT</sub> = 220μF, L = 15 μH

Ch1 : Vout,200mV/div,offset 3.3V Ch2 : Iout,1A/div,100mA-3A Ch2 rising time : 4us Ch2 falling time : 4us Time : 10us/div

comparator and compared with internal saw tooth wave. It generates a PWM control signal by the PWM comparator. The PWM signal feeds into the logic circuit and turns on or off the pass element. The Buck type output stage regulates the correct output voltage depends on the previous mechanism.

### **Current Limit**

The APW1172 monitors the current flow through the pass element and limits the maximum output current to prevent damages during overload or short-circuit conditions.

### **Over-Voltage Protection (OVP)**

The over voltage protection is realized by using an

# **Functional Description (Cont.)**

### Over-Voltage Protection (OVP) (Cont.)

internal comparator. The input of the OVP comparator connects to the feedback, that turns off the pass element when the OVP threshold is reached. This threshold is typically 25% higher than the feedback voltage.

### **Thermal protection**

The thermal protection function generates a control signal to shut off the APW1172. It prevents the damages caused by over heat situation. The thermal function was acted when the temperature of chip reaching 160°C. A hysteresis of the thermal protection function is approximately 30°C, in order to avoid pass element turns on and off immediately.

### Voltage Feed Forward

The Voltage Feed Forward is acting when VCC goes higher than 10V. This will increases the upper bond of the internal sawtooth wave and results duty keeping constant. The change of the upper bond is linear and proportion with VCC.

### current limit function acting and VOUT dropping. This results the switching frequency decreased. In the practical application, when the load current increase big enough such that current limit occurring. In this situation,more load current cause the output voltage get away the regulatory point and begin dropping until it's limitation. In this time, the actual duty was very small in general. But the on time period limited by the minimum on time limitation of the control circuit. This on time limitation induce the load current runs away the limiting boundary. To prevent this drawback, the frequency fold back is used to ensure that load current was limited by the setup value.

### **Inhibit Function**

The Inhibit function disables when the Inhibit voltage lower than 1.3V. APW1172 entered the standby mode with Inhibit voltage higher than 1.4V. The quiescent current in the standby mode is less than 100uA to saving power. If the Inhibit pin left floating, the Inhibit voltage will be pull up by internal current source.

### **Frequency Fold Back**

The Frequency Fold Back function acts when both the

### **Application Description**

### **Input Capacitor**

The APW1172 requires proper input capacitors to supply current surge during stepping load transients to prevent the input rail from dropping. Due to the wide range of input voltage, the input capacitor must be able to support the input operating voltage. Ultra-low-ESR capacitors, such as ceramic chip capacitors, are very good for the input capacitors. An aluminum electrolytic capacitor(>100 $\mu$ F, ESR<300m $\Omega$ ) is recommended as the input capacitor. It is not

necessary to use low-ESR capacitors. More capacitance reduce the variations of the input voltage of VCC pin.

### Inductor

Inductor is an important component in the application. In the switching regulator, energy stored in the inductor by magnetic field when the pass element conducting. This behavior cause the ripple current cycle by cycle, the ripple current flowing through the

#### Inductor (Cont.)

output capacitor induce the output ripple voltage. In general, the ripple current is usually fixed at 20%~40% of maximum output current, that is 0.6A~1.2A with maximum output current equal 3A. The value of inductor can approximate by (1)

$$L = \frac{V_{IN} - V_{CE} - V_o}{\Delta I} T_{on} \tag{1}$$

Where  $V_{IN}$  is the input voltage,  $V_{CE}$  is the voltage across the pass element when it conduct,  $V_{O}$  is the output voltage,  $\Delta I$  is the ripple current flowing through the inductor and Ton is the on period that determined by  $V_{O}$  and  $V_{IN}$ . The exact Ton can obtained by (2) and (3)

$$D = \frac{V_{O} + V_{D}}{V_{IN} - V_{CE} + V_{D}}$$

(2)

Where VD is the forward voltage of the wheeling diode.

$$T_{on} = DT_{S} \tag{3}$$

Where T<sub>s</sub> is the period of whole cycle. It equal 1/F<sub>s</sub> where F<sub>s</sub> is the switching frequency of APW1172. For example, V<sub>IN</sub> = 12V, V<sub>o</sub> = 3.3V, V<sub>D</sub> = 0.7V, I<sub>o</sub> = 3A, ripple current is I<sub>o</sub> (20%~40%) = 0.6A ~ 1.2A, V<sub>CE</sub> = 1.2V, F<sub>s</sub> = 250KHz

$$D = \frac{3.3V + 0.7V}{12V - 1.2V + 0.7V} = 34.78\% \qquad \text{by (2)}$$

$$T_{on} = DT_s = 34.78\% \times 4\mu s = 1.3912\mu s$$

by (3)

For the worst case ripple current equal 0.6A ~ 1.2A

$$L_{I} = \frac{12V - 1.2V - 3.3V}{0.6A} 1.3912 \mu s = 17.39 \mu H$$

for ripple current is 0.6A..... by (1)

$$L_{2} = \frac{12V - 1.2V - 3.3V}{1.2A} 1.3912 \mu s = 8.695 \mu H$$

for ripple current is 1.2A..... by (1)

Use the worst case to approximate the minimum value of inductor. In worst ripple current condition, smaller

dimension of inductor to save the board space. In other way, devote the performance by higher ripple current. If select a greater inductor, the ripple current will be smaller and a better performance is got. This tradeoff is an useful method to decide a better performance or a smaller inductor size.

#### **Output Capacitor**

The APW1172 requires a proper output capacitor to maintain stability and improve transient response over temperature and current. The output capacitor selection is dependent upon ESR (equivalent series resistance) and capacitance of the output capacitor over the operating temperature.

Consider the output ripple voltage that absorbed in the application.Output ripple voltage consist of two parts.It show as (4)

$$V_{ripple} = V_1 + V_2 \tag{4}$$

In previously, use the parameter  $\Delta I$  to decide the value of the inductor. As the same manner, use the parameter  $\Delta I$  to approximate the value of output capacitor.

The first part of output ripple voltage,V1,is related to the ESR of output capacitor.It show as (5)

$$V_1 = ESR \times \Delta I \tag{5}$$

The second part of output ripple voltage,V<sub>2</sub>,can calculated by (6)

$$V_2 = \frac{\Delta I}{8C} T_s \tag{6}$$

These two parameters determine the value of output ripple voltage and the efficiency. More output ripple voltage cause the efficiency decreased. The output ripple voltage means the energy loss in the ESR and the energy loss in the transition path while the energy stored and removed in the output capacitor. In other aspect, the ESR and the value of output capacitor

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

#### **Output Capacitor (Cont.)**

generate a zero to provide a positive phase for control loop. This zero improved the stability without extra PID compensator, if the zero is lower enough.

#### Switch diode

APW1172 is an non-synchronous type buck regulator and needs a Shottky diode as the wheeling diode. This diode will conduct when the pass element turned off.Current flows through the diode in the conducted period, the order of the maximum peak current reaches few Amperes. The diode requires the ability to flow the great forward current. The peak forward current of the diode denote in the specification must great than 15A, and the conducting time in this situation must great than 8ms. 1N5818 is a suitable component.

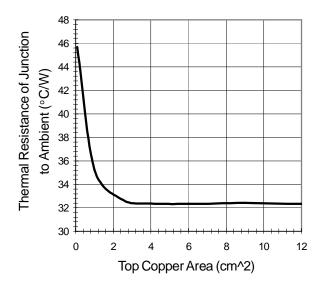

#### **Thermal Consideration**

APW1172 is a switching regulator whose pass element inside, it have the ability to provide 3 Amperes. As the show in the block diagram, the structure of the pass element consist of a NPN and a PNP transistors. The voltage across the pass element, VCE, is about 0.8V to 1.3V in the light load to heavy load. The product of VCE and IL, where IL is current flowing through the inductor, generate thermal cause the junction temperature increased. The thermal stream conduct via the thermal pad of SOP-8-P to the printed circuit board.The power dissipation of APW1172 can be approximated by (7)

$$P = (V_{CE} \times I_L \times D) + (V_{IN} \times I_L \times F_S)(T_R + T_F)$$

(7)

Where  $V_{CE}$  is the voltage across the pass element,  $I_L$  is the current flowing through the inductor, D is the duty. TR and TF are the transition time.

The wheeling diode is another thermal source. It's power dissipation approximated by (8)

$$P_D = V_D \times I_D \times (1 - D) \tag{8}$$

Where VD is the forward voltage of the wheeling diode, ID is current flowing through the wheeling diode when it conducting. In the PCB layout, usually place the wheeling diode near the APW1172, the power dissipation of wheeling diode will increase the ambient temperature and limit the maximum power dissipation of APW1172. These power dissipations are the major energy loss in the voltage conversion.

To improve the thermal resistance by increasing copper area is a suitable method. Design a copper area according to the following curve to improve the thermal resistance.

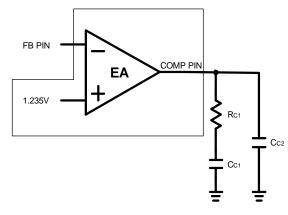

### **Frequency Compensation**

In the Buck converter, there is a LPF (Low Pass Filter) in the output stage to filtering the switching noise. The LPF consist of an inductor and a capacitor. These two components generate the double poles in the frequency domain.

$$f_{natural} = \frac{1}{2\boldsymbol{p}\sqrt{LC}}$$

Where L is the inductance of the LPF and C is the capacitance of the output capacitor. These double poles

Copyright @ ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

(9)

#### Frequency Compensation (Cont.)

cause the phase decrease rapidly at the natural frequency and lead the phase margin not enough to maintain the stable status. The stable issue improved by apply a zero in the frequency domain to increase the phase margin.

Adding a resistor and a capacitor at the COMP pin is the simplest way to generate a zero. The placement of the components is the show of Figure-1. The frequency of the zero is

$$f_{zero} = \frac{1}{2pR_{c1}C_{c1}}$$

(10)

The relation of the zero and the natural frequency is

$$f_{zero} = 0.8 \cdot f_{natural} \tag{11}$$

Locate the zero before the natural frequency to compensate the phase. The another capacitor Cc2 used to bypass the noise. In general

$$C_{C2} = \frac{1}{10} C_{C1} \tag{12}$$

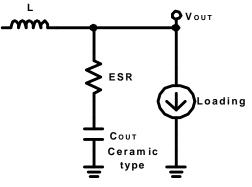

In the other applications, use the ceramic capacitor as the output capacitor is very popular. Because the small dimension of the ceramic capacitor save the PCB (Printed Circuit Board) area, the low ESR (Equivalent Series Resistance) of the ceramic one decrease the power dissipation of the output capacitor. But the serious drawbacks of the ceramic one is the stable issue.

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

Consider the Figure-2, find the transfer function H (s) as:

$$H(s) = \frac{SC_{OUT}(ESR) + 1}{S^2 LC_{OUT} + SC_{OUT}(ESR) + 1}$$

$$pole_{1,2} = \frac{1}{2\pi\sqrt{LC_{OUT}}}$$

$$zero_1 = \frac{1}{2\pi(ESR)C_{OUT}}$$

$$Q = \frac{1}{(ESR)}\sqrt{\frac{L}{C_{OUT}}}$$

The pole1 and pole2 are the conjugate roots of the denominator and the zero1 is the root of the numerator. Find the Q factor from the quadratic function and the description of Q factor as above.

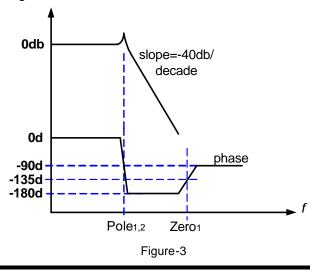

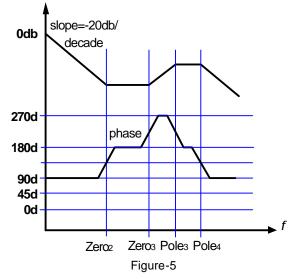

The frequency response of the output stage show as Figure-3.

#### Frequency Compensation (Cont.)

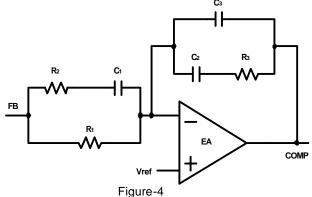

The problem is the phase nearly –180 degrees at the natural frequency especially in the high Q situation. If the Q factor is high, the phase decrease vary sharp at the location of the double poles. This problem leads the regulator oscillating when use ceramic one as the output capacitor without compensation. The purpose of the compensation is saving the phase. The manner is added additional zeros to achieve the goal. A zero have the ability that contribute the maximum phase of 90 degrees. According this characteristic, needs two zeros to compensate the phase loss. The PID compensator is good for this.It shows as Figure-4.

The transfer function H(s) is

$$H(s) = \frac{(SC_2R_3 + 1)[SC_1(R_1 + R_2) + 1]}{S(SC_1R_2 + 1)[SC_2C_3R_3 + (C_2 + C_3)]}$$

$$zero_2 = \frac{1}{2\mathbf{p} \cdot C_2R_3}$$

$$zero_3 = \frac{1}{2\mathbf{p} \cdot C_1(R_1 + R_2)}$$

$$pole_3 = \frac{1}{2\mathbf{p} \cdot C_1R_2}$$

$$pole_4 = \frac{C_2 + C_3}{2\mathbf{p} \cdot C_2C_3R_3}$$

The frequency response of the PID compensator pre-

sented as Figure-5:

The assumption is 10(zero2)<zero3,10(zero3)<pole3, 10(pole3)<pole4.In order to compensate the phase, place the two zeros closely and located before the natural frequency. In general

$$zero_2 \cong zero_3 = k \cdot pole_{1,2}$$

(11)

Where k is a constant, the value of k is almost 0.7 to 0.8.

The useful rules are:

(1) Determine the value of C2, the value must smaller than 5nF to get fast response time.

(2) Find R3 by the equation

$$R_3 = (2\boldsymbol{p} \cdot \boldsymbol{C}_2 \cdot \boldsymbol{k} \cdot pole_{1,2})^{-1}$$

(3) Determine the value of C1 from 470pF to 1uF. This range of C1 is for reference.

(4) The range of pole3 is from 150KHz to 300KHz. Use this range to find the value of R2.

(5) Find R1 by the equation

$$R_1 = (2\pi \cdot C_1 \cdot k \cdot pole_{1,2})^{-1} - R_2$$

(6) The location of pole4 is 5 times pole3. Use this result to find the value of R3.

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

## Layout Consideration

1. Please solder the Exposed Pad on the PCB. The heat generated by the power consumption will conduct by the thermal pad.

- 2. Please place the input capacitors for VCC pin nearly as close as possible.

- 3. Connect the switching inductor and the Schottky diode and OUT pin by a wide track.

- 4. Place the output capacitor close to the inductor as possible and with a wide and short track.

- 5. The thermal pad is needed to improve the power dissipation.

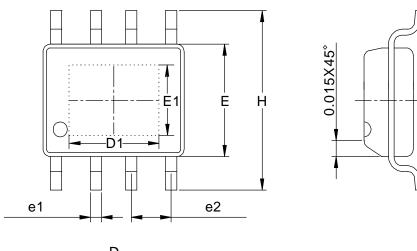

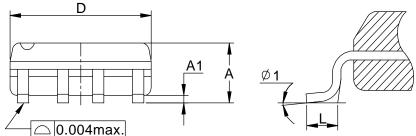

# Packaging Information

SOP-8-P pin (Reference JEDEC Registration MS-012)

| Dim | Millim | neters     | Inch  | nes   |

|-----|--------|------------|-------|-------|

| Dim | Min.   | Max.       | Min.  | Max.  |

| A   | 1.35   | 1.75       | 0.053 | 0.069 |

| A1  | 0      | 0.15       | 0     | 0.006 |

| D   | 4.80   | 5.00       | 0.189 | 0.197 |

| D1  | 3.00   | 3.00REF 0. |       | REF   |

| E   | 3.80   | 4.00       | 0.150 | 0.157 |

| E1  | 2.60   | REF        | 0.102 | REF   |

| Н   | 5.80   | 6.20       | 0.228 | 0.244 |

| L   | 0.40   | 1.27       | 0.016 | 0.050 |

| e1  | 0.33   | 0.51       | 0.013 | 0.020 |

| e2  | 1.27   | 1.27BSC    |       | BSC   |

| φ1  | 8      | <b>8</b> ° |       | o     |

# **Physical Specifications**

| Terminal Material  | Solder-Plated Copper (Solder Material : 90/10 or 63/37 SnPb), 100%Sn |

|--------------------|----------------------------------------------------------------------|

| Lead Solderability | Meets EIA Specification RSI86-91, ANSI/J-STD-002 Category 3.         |

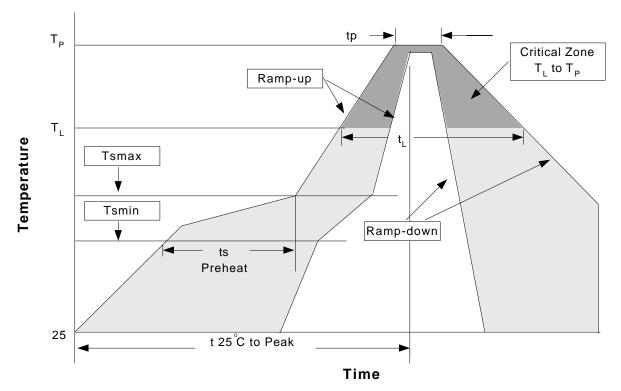

### Reflow Condition (IR/Convection or VPR Reflow)

### **Classification Reflow Profiles**

| Profile Feature                                                                               | Sn-Pb Eutectic Assembly          | Pb-Free Assembly                 |  |

|-----------------------------------------------------------------------------------------------|----------------------------------|----------------------------------|--|

| Average ramp-up rate $(T_1 \text{ to } T_P)$                                                  | 3°C/second max.                  | 3°C/second max.                  |  |

| Preheat<br>- Temperature Min (Tsmin)<br>- Temperature Max (Tsmax)<br>- Time (min to max) (ts) | 100°C<br>150°C<br>60-120 seconds | 150°C<br>200°C<br>60-180 seconds |  |

| Time maintained above:<br>- Temperature (T <sub>L</sub> )<br>- Time (t <sub>L</sub> )         | 183°C<br>60-150 seconds          | 217°C<br>60-150 seconds          |  |

| Peak/Classificatioon Temperature (Tp)                                                         | See table 1                      | See table 2                      |  |

| Time within 5°C of actual<br>Peak Temperature (tp)                                            | 10-30 seconds                    | 20-40 seconds                    |  |

| Ramp-down Rate                                                                                | 6°C/second max.                  | 6°C/second max.                  |  |

| Time 25°C to Peak Temperature                                                                 | 6 minutes max.                   | 8 minutes max.                   |  |

| Note: All temperatures refer to topside of the package .Measured on the body surface.         |                                  |                                  |  |

Copyright © ANPEC Electronics Corp. Rev. A.4 - Aug., 2005

## Classification Reflow Profiles(Cont.)

#### Table 1. SnPb Entectic Process – Package Peak Reflow Temperatures

| Package Thickness | Volume mm <sup>3</sup><br><350 | Volume mm <sup>3</sup><br>³350 |

|-------------------|--------------------------------|--------------------------------|

| <2.5 mm           | 240 +0/-5°C                    | 225 +0/-5°C                    |

| ≥2.5 mm           | 225 +0/-5°C                    | 225 +0/-5°C                    |

Table 2. Pb-free Process – Package Classification Reflow Temperatures

| Package Thickness                                                                         | Volume mm <sup>3</sup><br><350                                                                   | Volume mm <sup>3</sup><br>350-2000 | Volume mm <sup>3</sup><br>>2000 |  |  |  |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|--|--|--|

| <1.6 mm                                                                                   | 260 +0°C*                                                                                        | 260 +0°C*                          | 260 +0°C*                       |  |  |  |

| 1.6 mm – 2.5 mm                                                                           | 260 +0°C*                                                                                        | 250 +0°C*                          | 245 +0°C*                       |  |  |  |

| ≥2.5 mm                                                                                   | 250 +0°C*                                                                                        | 245 +0°C*                          | 245 +0°C*                       |  |  |  |

| *Tolerance: The device m                                                                  | *Tolerance: The device manufacturer/supplier <b>shall</b> assure process compatibility up to and |                                    |                                 |  |  |  |

| including the stated classification temperature (this means Peak reflow temperature +0°C. |                                                                                                  |                                    |                                 |  |  |  |

| For example 260°C+0°C                                                                     | c) at the rated MSL level.                                                                       |                                    |                                 |  |  |  |

# Reliability test program

| Test item     | Method              | Description                    |

|---------------|---------------------|--------------------------------|

| SOLDERABILITY | MIL-STD-883D-2003   | 245°C , 5 SEC                  |

| HOLT          | MIL-STD-883D-1005.7 | 1000 Hrs Bias @ 125 °C         |

| PCT           | JESD-22-B, A102     | 168 Hrs, 100 % RH , 121°C      |

| TST           | MIL-STD-883D-1011.9 | -65°C ~ 150°C, 200 Cycles      |

| ESD           | MIL-STD-883D-3015.7 | VHBM > 2KV, VMM > 200V         |

| Latch-Up      | JESD 78             | 10ms , I <sub>tr</sub> > 100mA |

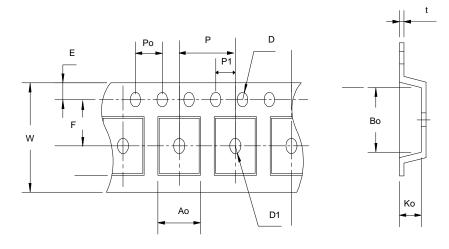

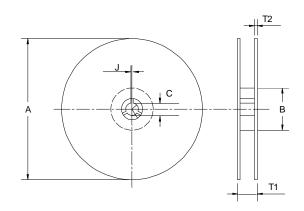

### **Carrier Tape**

## Carrier Tape(Cont.)

| Application | А           | В            | С          | J           | T1          | T2          | W        | Р       | E              |

|-------------|-------------|--------------|------------|-------------|-------------|-------------|----------|---------|----------------|

| SOP-8-P     | 330±1       | $62 \pm 1.5$ | 12.75 +    | 2 + 0.5     | 12.4 +0.2   | 2± 0.2      | 12 + 0.3 | 8± 0.1  | $1.75 \pm 0.1$ |

|             |             |              | 0.1 5      |             |             |             | - 0.1    |         |                |

| Application | F           | D            | D1         | Po          | P1          | Ao          | Bo       | Ko      | t              |

| SOP-8-P     | $5.5\pm0.1$ | 1.55±0.1     | 1.55+ 0.25 | $4.0\pm0.1$ | $2.0\pm0.1$ | $6.4\pm0.1$ | 5.2± 0.1 | 2.1±0.1 | 0.3±0.013      |

|             |             |              |            |             |             |             |          |         |                |

(mm)

### **Cover Tape Dimensions**

| Application | Carrier Width | Cover Tape Width | Devices Per Reel |

|-------------|---------------|------------------|------------------|

| SOP- 8-P    | 12            | 9.3              | 2500             |

### **Customer Service**

#### Anpec Electronics Corp.

Head Office :

5F, No. 2 Li-Hsin Road, SBIP,

Hsin-Chu, Taiwan, R.O.C.

Tel: 886-3-5642000

Fax: 886-3-5642050

Taipei Branch :

7F, No. 137, Lane 235, Pac Chiao Rd., Hsin Tien City, Taipei Hsien, Taiwan, R. O. C. Tel : 886-2-89191368

Fax: 886-2-89191369